# CDP1821C/3

# **High-Reliability CMOS** 1024-Word x 1-Bit Static RAM

March 1997

### **Features**

- Static CMOS Silicon-On-Sapphire Circuitry CD4000-Series Compatible

- Compatible with CDP1800-Series Microprocessors at **Maximum Speed**

- Fast Access Time. . . . . . . . . 100ns Typ. at V<sub>DD</sub> = 5V

- Single Voltage Supply

- . No Precharge or External Clocks Required

- · Low Quiescent and Operating Power

- Separate Data Inputs and Outputs

- Memory Retention for Standby Battery Voltage Down to 2V at +25°C

- Latch-Up-Free Transient-Radiation Tolerance

# Ordering Information

| PACKAGE | TEMP. RANGE     | PART<br>NUMBER | PKG. NO. |

|---------|-----------------|----------------|----------|

| SBDIP   | -55°C to +125°C | CDP1821CD3     | D16.3    |

# Description

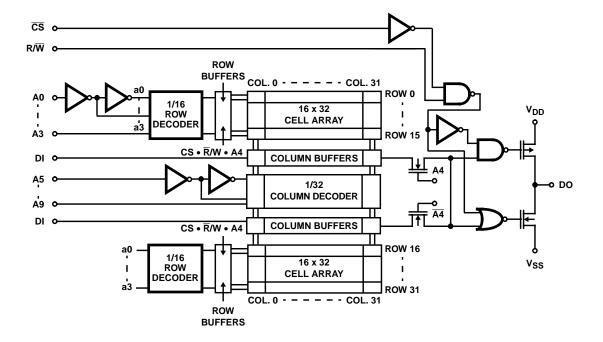

The CDP1821C/3 is a 1024-word x 1-bit CMOS silicon-on-sapphire (SOS), fully static, random-access memory designed for use in CDP1800 microprocessor systems. This device has a recommended operating voltage range of 4V to 6.5V.

The output state of the CDP1821C/3 is a function of the input address and chip-select states only. Valid data will appear at the output in one access time following the latest address change to a selected chip. After valid data appears, the address may be changed immediately. It is not necessary to clock the chip-select input or any other input terminal for fully static operation; therefore the chip-select input may be used as an additional address input. When the device is in an unselected state ( $\overline{CS} = 1$ ), the internal write circuitry and output sense amplifier are disabled. This feature allows the three-state data outputs from many arrays to be OR-tied to a common bus for easy memory expansion.

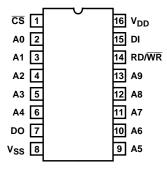

### **Pinout**

CDP1821C/3 (SBDIP) **TOP VIEW**

# Functional Block Diagram

# **OPERATIONAL MODES**

|         | INPUTS                        |   | OUTPUT                     |

|---------|-------------------------------|---|----------------------------|

| MODE    | READ/WRITE CHIP-SELECT R/W CS |   | DATA OUTPUT DO             |

| Standby | Х                             | 1 | High Impedance             |

| Write   | 0                             | 0 | High Impedance             |

| Read    | 1                             | 0 | Contents of Addressed Call |

X = Don't Care Logic 1 = High Logic 0 = Low

# CDP1821C/3

# **Absolute Maximum Ratings**

# DC Supply Voltage Range, (V<sub>DD</sub>) (All Voltages Referenced to VSS Terminal).....-0.5V to +7V Input Voltage Range, All Inputs .....-0.5V to V<sub>DD</sub> +0.5V DC Input Current, Any One Input.....±10mA

# **Thermal Information**

| Thermal Resistance (Typical)          | θ <sub>JA</sub> (°C/W) | $\theta_{JC}$ ( $^{\circ}C/W$ ) |

|---------------------------------------|------------------------|---------------------------------|

| SBDIP Package                         | 75                     | 20                              |

| Maximum Operating Temperature Range   | $(T_A) \dots -55^{C}$  | C to +125°C                     |

| Maximum Storage Temperature Range (T  | 65 <sup>c</sup>        | °C to +150°C                    |

| Maximum Lead Temperature (During Solo | dering)                | +265 <sup>o</sup> C             |

| Maximum Junction Temperature          |                        | +150 <sup>o</sup> C             |

$\textbf{Recommended Operating Conditions} \quad \textbf{T}_{A} = \textbf{Full Package-Temperature Range}. \ \textbf{For maximum reliability, nominal operating constraints} \\ \textbf{T}_{A} = \textbf{Full Package-Temperature Range}. \\ \textbf{T}_{A} = \textbf{T}_{A} = \textbf{T}_{A} + \textbf{$ ditions should be selected so that operation is always within the following ranges:

|                            | CDP18           |                 |       |

|----------------------------|-----------------|-----------------|-------|

| PARAMETER                  | MIN             | MAX             | UNITS |

| DC Operating Voltage Range | 4               | 6.5             | V     |

| Input Voltage Range        | V <sub>SS</sub> | V <sub>DD</sub> | V     |

# Static Electrical Specifications $V_{DD} = 5V \pm 5\%$

|                                             |                  |                                  | -55°C, +25°C         |                     | +12                  | 5°C                 |       |

|---------------------------------------------|------------------|----------------------------------|----------------------|---------------------|----------------------|---------------------|-------|

| PARAMETER                                   | SYMBOL           | CONDITIONS                       | MIN                  | MAX                 | MIN                  | MAX                 | UNITS |

| Quiescent Device Current (Note 1)           | I <sub>DD</sub>  | $V_{IN} = 0V \text{ or } V_{DD}$ | -                    | 260                 | -                    | 1000                | μΑ    |

| Output Low Drive (Sink) Current (Note 1)    | l <sub>OL</sub>  | V <sub>OUT</sub> = 0.4V          | 2.7                  | -                   | 1.6                  | -                   | mA    |

| Output High Drive (Source) Current (Note 1) | I <sub>ОН</sub>  | $V_{OUT} = V_{DD} - 0.4V$        | -1.3                 | -                   | -0.8                 | -                   | mA    |

| Output Voltage Low-Level                    | V <sub>OL</sub>  | -                                | -                    | 0.1                 | -                    | 0.5                 | V     |

| Output Voltage High-Level                   | Voн              | -                                | V <sub>DD</sub> -0.1 | -                   | V <sub>DD</sub> -0.5 | -                   | V     |

| Input Low Voltage                           | V <sub>IL</sub>  | -                                | -                    | 0.3 V <sub>DD</sub> | -                    | 0.3 V <sub>DD</sub> | V     |

| Input High Voltage                          | V <sub>IH</sub>  | -                                | 0.7 V <sub>DD</sub>  | -                   | 0.7 V <sub>DD</sub>  | -                   | V     |

| Input Current (Note 1)                      | I <sub>IN</sub>  | $V_{IN} = 0V \text{ or } V_{DD}$ | -                    | 2.6                 | -                    | 10                  | μΑ    |

| Three-State Output Leakage Current (Note 1) | lout             | $V_{IN} = 0V \text{ or } V_{DD}$ | -                    | 2.6                 | -                    | 10                  | μΑ    |

| Operating Current (Note 2)                  | I <sub>DD1</sub> | -                                | -                    | 5                   | -                    | 10                  | mA    |

| Input Capacitance                           | C <sub>IN</sub>  | -                                | -                    | 7.5                 | -                    | 7.5                 | pF    |

| Output Capacitance                          | C <sub>OUT</sub> | -                                | -                    | 15                  | -                    | 15                  | pF    |

### NOTES:

- 1. Limits designate 100% testing. All other limits are designer's parameters under given test conditions and do not represent 100% testing

- 2. Measured with  $1\mu s$  read-cycle time and outputs floating.

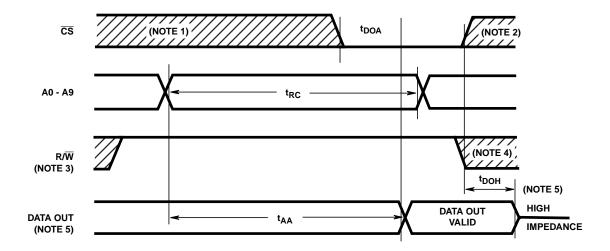

Read Cycle Dynamic Electrical Specifications  $t_R$ ,  $t_F$  = 10ns,  $C_L$  = 50pF

|                           |                  | V <sub>DD</sub> | -55 <sup>o</sup> C, | +25°C | +12 | 5°C |       |

|---------------------------|------------------|-----------------|---------------------|-------|-----|-----|-------|

| PARAMETER                 | SYMBOL           | (V)             | MIN                 | MAX   | MIN | MAX | UNITS |

| Data Access Time (Note 1) | t <sub>DA</sub>  | 5               | -                   | 190   | -   | 255 | ns    |

| Read Cycle Time           | t <sub>RC</sub>  | 5               | 190                 | -     | 255 | -   | ns    |

| Output Enable Time        | t <sub>EN</sub>  | 5               | 65                  | -     | 90  | -   | ns    |

| Output Disable Time       | t <sub>DIS</sub> | 5               | -                   | 65    | -   | 90  | ns    |

### NOTE:

1. 100% testing. All other limits are designer's parameters under given test conditions and do not represent 100% testing.

### NOTES:

- 1. Chip-Select  $(\overline{CS})$  permitted to change from high to low level or remain low on a selected device.

- 2. Chip-Select  $(\overline{\text{CS}})$  permitted to change from low to high level or remain low.

- 3. Read/Write  $(R/\overline{W})$  must be at a high level during all address transitions.

- 4. Don't care.

- 5. Data-Out (DO) is a high impedance within  $t_{DIS}$  ns after the falling edge of  $R/\overline{W}$  or the rising edge of  $\overline{CS}$ .

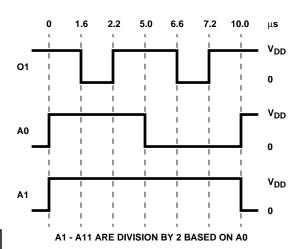

FIGURE 1. READ CYCLE TIMING DIAGRAM

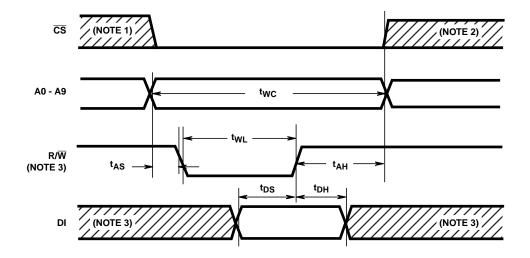

Write Cycle Dynamic Electrical Specifications  $t_R$ ,  $t_F$  = 10ns,  $C_L$  = 50pF

|                                     |                 | V <sub>DD</sub> | -55 <sup>o</sup> C, | +25°C | +12 | 5°C |       |

|-------------------------------------|-----------------|-----------------|---------------------|-------|-----|-----|-------|

| PARAMETER                           | SYMBOL          | (V)             | MIN                 | MAX   | MIN | MAX | UNITS |

| Write Cycle Time                    | t <sub>WC</sub> | 5               | 300                 | -     | 420 | -   | ns    |

| Address Setup Time (Note 1)         | t <sub>AS</sub> | 5               | 60                  | -     | 84  | -   | ns    |

| Address Hold Time (Note1)           | t <sub>AH</sub> | 5               | 130                 | -     | 180 | -   | ns    |

| Input Data Setup Time (Note 1)      | t <sub>DS</sub> | 5               | 90                  | -     | 125 | -   | ns    |

| Input Data Hold Time (Note 1)       | t <sub>DH</sub> | 5               | 60                  | -     | 84  | -   | ns    |

| Read/Write Pulse Width Low (Note 1) | t <sub>WL</sub> | 5               | 110                 | -     | 155 | -   | ns    |

### NOTE:

1. 100% testing. All other limits are designer's parameters under given test conditions and do not represent 100% testing.

### NOTES:

- 1. Chip-Select  $(\overline{CS})$  permitted to change from high to low level or remain low on a selected device.

- 2. Chip-Select  $(\overline{CS})$  permitted to change from low to high level or remain low.

- 3. Don't care.

FIGURE 2. WRITE CYCLE TIMING DIAGRAM

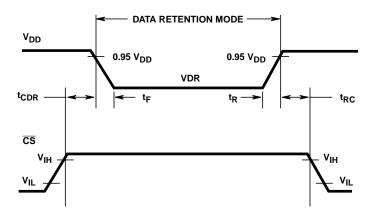

# **Data Retention Specifications**

|                                           |                 | TEST CO                | NDITIONS               | -55 <sup>o</sup> C, | +25°C | +12 | 5°C |       |

|-------------------------------------------|-----------------|------------------------|------------------------|---------------------|-------|-----|-----|-------|

| PARAMETER                                 | SYMBOL          | V <sub>DR</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN                 | MAX   | MIN | MAX | UNITS |

| Minimum Data Retention Voltage (Note 1)   | V <sub>DD</sub> | -                      | -                      | -                   | 2     | -   | 2.5 | V     |

| Data Retention Quiescent Current (Note 1) | I <sub>DD</sub> | 2                      | -                      | -                   | 50    | -   | 200 | μΑ    |

| Chip Deselect to Data Retention Time      | tCDR            | -                      | 5                      | 450                 | -     | 650 | -   | ns    |

| Recovery to Normal Operation Time         | t <sub>RC</sub> | -                      | 5                      | 450                 | -     | 650 | -   | ns    |

# NOTE:

1. 100% testing. All other limits are designer's parameters under given test conditions and do not represent 100% testing

FIGURE 3. LOW  $\mbox{V}_{\mbox{\scriptsize DD}}$  data retention waveforms and timing diagram

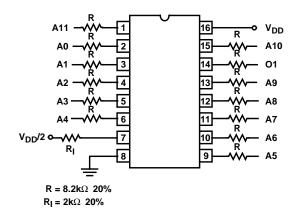

# **Burn-In Circuit**

| PACKAGE | V <sub>DD</sub> | TEMPERATURE         | DURATION |

|---------|-----------------|---------------------|----------|

| D       | 7V              | +125 <sup>0</sup> C | 160 Hrs. |

FIGURE 4. DYNAMIC/OPERATING BURN-IN CIRCUIT AND TIMING DIAGRAM

# CDP1821C/3

|                                                                              |                                                                                                     | bled and tested under ISO9000 quality systems of                                                                                                                                                                                                                                  |                  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| notice. Accordingly, the reader is can and reliable. However, no responsible | utioned to verify that data sheets are current<br>lity is assumed by Intersil or its subsidiaries f | right to make changes in circuit design and/or specifications at<br>before placing orders. Information furnished by Intersil is believe<br>or its use; nor for any infringements of patents or other rights of the<br>ny patent or patent rights of Intersil or its subsidiaries. | d to be accurate |

|                                                                              | <u> </u>                                                                                            | ts products, see web site http://www.intersil.com                                                                                                                                                                                                                                 |                  |

| Sales Office Headq                                                           |                                                                                                     |                                                                                                                                                                                                                                                                                   |                  |

| NORTH AMERICA Intersil Corporation                                           | EUROPE<br>Intersil SA                                                                               | <b>ASIA</b><br>Intersil (Taiwan) Ltd.                                                                                                                                                                                                                                             |                  |

P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000

FAX: (407) 724-7240

Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029