## Microprocessor/Memory **Applications Briefs**

A compendium of the most useful CDP1800 Series microprocessor/memory application hints that have appeared in recent issues of the RCA Solid State Newsietter.

Solid

State

Brussels • Buenos Aires • Hamburg

Montreal • Paris • Sao Paulo • Some

Sunbury-on-Thames • Taipei • Tokyo Montreal • Paris • Sao Paulo • Somerville NJ • Stockholm

#### INTRODUCTION

This manual is an outgrowth of application-related activities at RCA as they pertain to the needs of our 1800 Series customer base. The inputs for the articles have come directly from customers, indirectly through our field sales and applications force, and as a spinoff of new product definition work. Because of this, these briefs should answer application-type questions that may not be sufficiently explained in our current product literature. New material will periodically update this publication, and, as subject material expands, articles about specific device types will be combined into general Application Notes and appear in future Data Book releases.

We welcome your comments and suggestions for new mini-notes, based on your experiences in developing hardware and software around the 1800 series. We would appreciate it if you could pass along to your local RCA Representative any material that is not of a proprietary nature - we will consider developing any ideas that meet the general needs of our customer base.

## TABLE OF CONTENTS

| Page | CDP1802                                                                                                           |

|------|-------------------------------------------------------------------------------------------------------------------|

| 6    | <ul> <li>Oscillator Design Considerations for the CDP1802</li> </ul>                                              |

| 10   | <ul><li>Low Voltage Operation of the 1802</li></ul>                                                               |

| 11   | <ul> <li>Data Bus Contention During CDP1802 Register-to-Register Operations</li> </ul>                            |

| 12   | • 1802 Interrupt Control Circuits                                                                                 |

| 15   | <ul> <li>Using the 1802 Scratchpad to Store RAM Variables</li> </ul>                                              |

| 17   | <ul> <li>Optimizing Hardware/Software Trade-offs in CDP1802 Miroprocessor<br/>Applications (ICAN 6704)</li> </ul> |

| 27   | <ul> <li>CDP1802 Expanded Output Control Using the CD4099</li> </ul>                                              |

| 29   | • CDP1802 vs CDP1802A - Performance Enhancements                                                                  |

| 30   | ● 16-Bit Operations in the CDP1802 Microprocessor (ICAN 6842)                                                     |

|      | CDP1804/1805                                                                                                      |

| 35   | <ul> <li>CDP1804/05 - Improve System Performance and Lower Chip Count</li> </ul>                                  |

| 43   | • The New CDP1804A                                                                                                |

| 44   | ● The Expanded 1804 Instruction Set                                                                               |

| 54   | <ul> <li>A Brief 1804-8048 Architecture Comparison</li> </ul>                                                     |

| 56   | <ul> <li>CDP1805 Operation in the CDP18S030 Evaluation Kit</li> </ul>                                             |

| 57   | <ul> <li>Interrupt Control Logic in the CDP1805</li> </ul>                                                        |

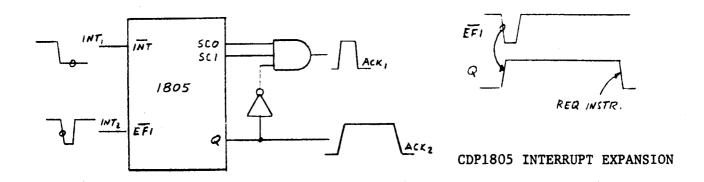

| 59   | <ul> <li>Adding a Second Interrupt to the CDP1805</li> </ul>                                                      |

| 61   | <ul> <li>Using the CDP1805 Timer-Counter for Multiple DMA Transfers</li> </ul>                                    |

| 63   | Multiple DMA Under Software Control                                                                               |

|      | CDP1851                                                                                                           |

| 65   | • Understanding the CDP1851 Programmable I/O                                                                      |

| 79   | Memory-Mapping the 1851                                                                                           |

## CDP1852

- 81 Using the CDP1852 I/O for DMA Operations

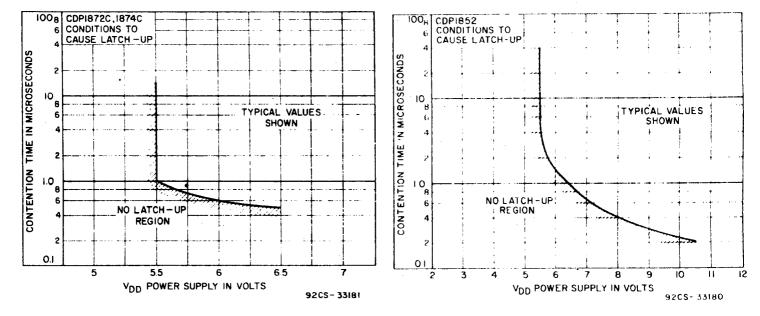

- 83 Bus Contention Effects for CMOS I/O Ports

#### Table of Contents (cont'd)

#### Page CDP1854A

- 84 1854A vs. 1854 Design Improvements for Higher System Speeds

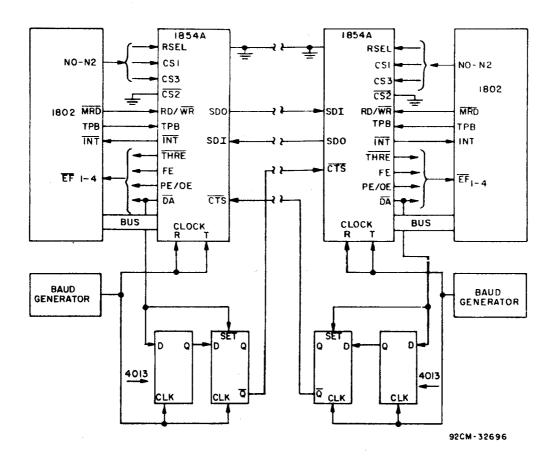

- 88 Interfacing Two COSMAC Systems Using 1854A UARTS

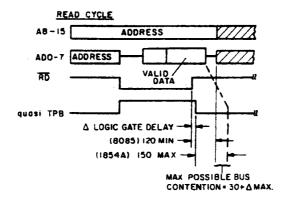

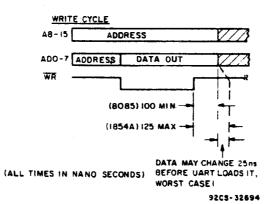

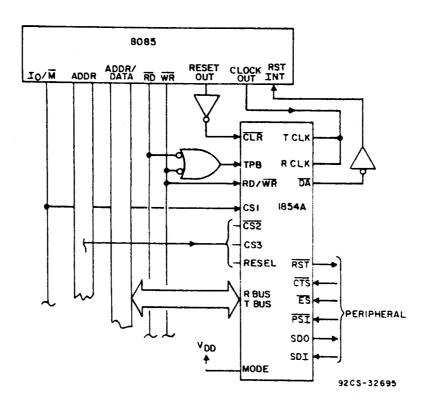

- 89 Interfacing the 1854A with the 8085

- 91 Competitive UARTS An Industry Comparison

#### CDP1855

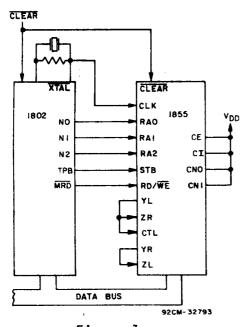

- 93 Using the MDU

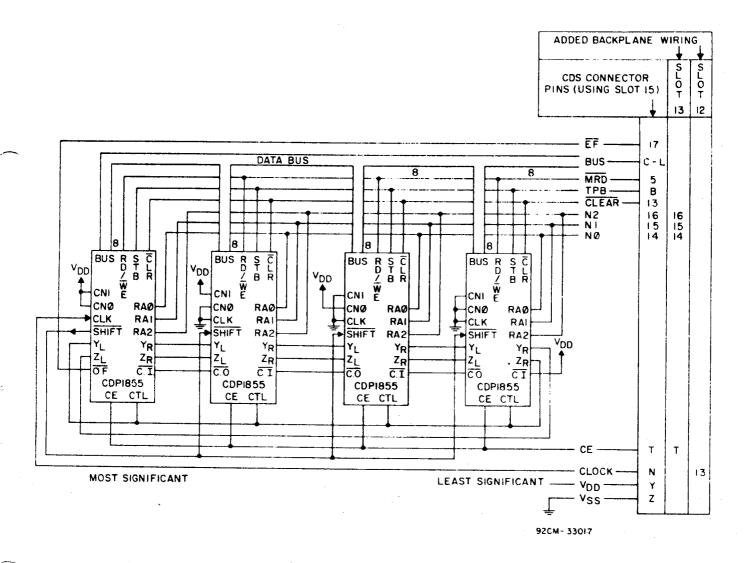

- 97 Interfacing a "Full House" MDU Board with the CDS

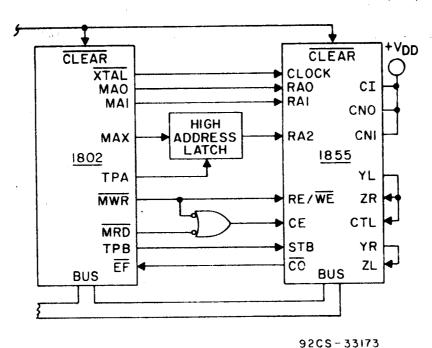

- 100 Memory-Mapping the MDU

- 101 Faster MDU Throughput Using "DMA Method"

- 106 Digital Filter Using the CDP1855

#### CDP1869/70/76

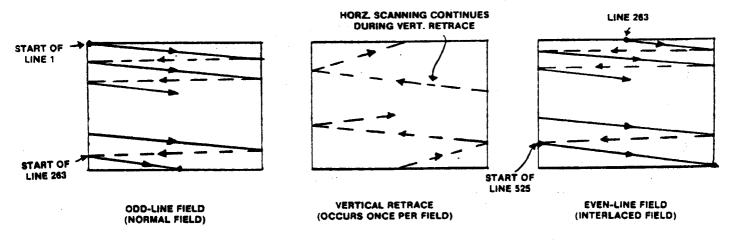

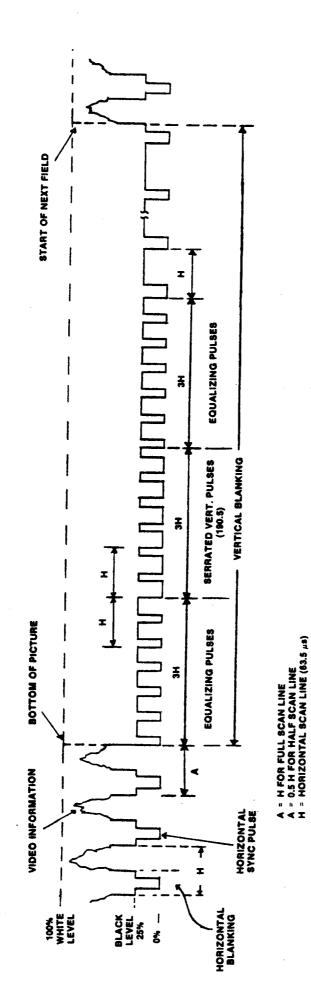

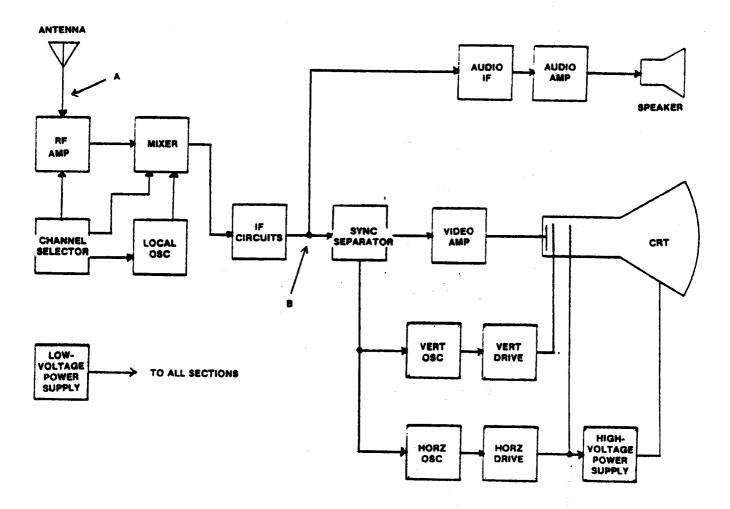

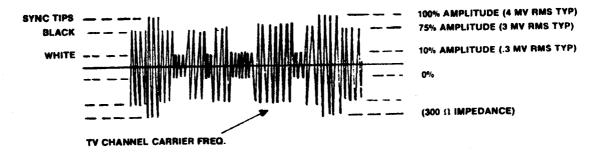

- 110 An Introduction to the Video Interface System Devices (ICAN 6953)

- 121 A Review of General Video Display Techniques

- 134 Using Slower Memories with the VIS Display System (ICAN 6889)

- 137 Technical and Marketing Position of VIS

#### CDP1871

143 • CDP1871 Keyboard Encoder Enhancements

#### CDP1822/MWS5101

- 147 A competitive Analysis of the 5101 CMOS Static RAM

- 151 Operating Current Derating Curves for the 256X4 RAM

#### Synchronous RAMS

- Synchronous vs. Asynchronous RAMS....Which is Better?

- 155 The Synchronous RAM Syndrome

#### ROMS

162 • Masked ROM Programming Instructions

#### Page Table of Contents (cont'd)

#### CDP18U42

- 168 CDP18U42-1702 EPROM Comparison

- 171 CDP18U42-IM6654 EPROM Comparison

- 174 CDP18U42 PROM Programmer Circuit Options

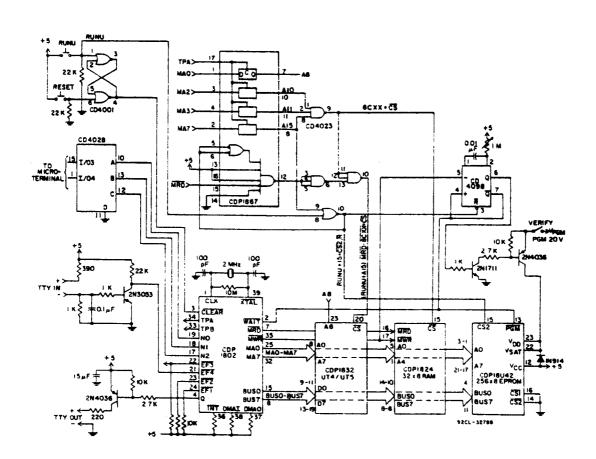

- 178 CDP1802-Based PROM Programmer Circuit for the CDP18U42 EPROM

#### Miscellaneous

181 • New Data Sheet Releases

#### Systems

- Pro-Log PROM Programmer Interface for COSMAC Development System II (ICAN 6622)

- 194 Interfacing PLM Code to CDOS System Functions (ICAN 6928)

- A Methodology for Programming COSMAC 1802 Applications Using Higher-Level Languages (ICAN 6918)

- Using the COSMAC Microboard Battery-Backup RAM, CDP18S622 (ICAN 6955)

- 209 Programming 2732 PROM's With The CDP18S480 PROM Programmer (ICAN 6847)

- 212 Cassette Tape I/O for COSMAC Microprocessor Systems (ICAN 6934)

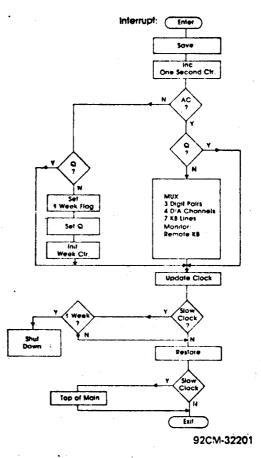

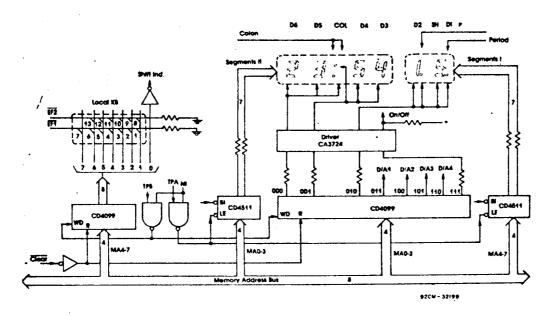

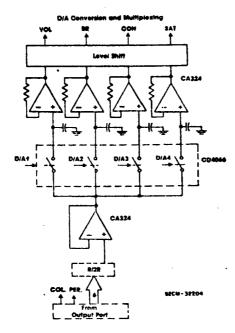

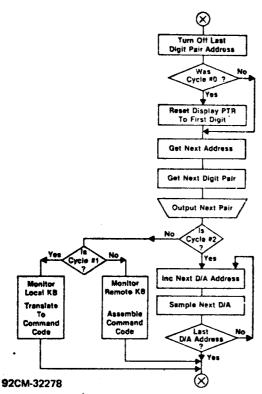

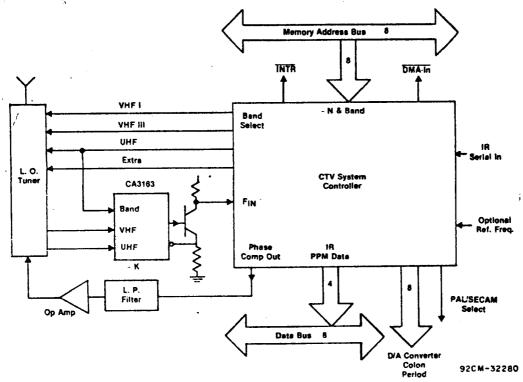

- Microprocessor Control for Color T.V. Receivers

- 5-

.

·

#### OSCILLATOR DESIGN CONSIDERATIONS FOR THE CDP1802

Despite the widespread use of crystal-controlled oscillators for microprocessors, crystal selection may still pose problems for many designers. Most of these problems can be minimized by an understanding of the various properties and specifications needed to define an oscillator circuit for the CDP1802 microprocessor.

#### Clock Frequency and Accuracy

Quartz crystal oscillators will provide frequency stability better than 0.01%. However, many microprocessor applications do not require an exact clock frequency — therefore, the use of RC or LC type oscillators may be a wise cost-effective choice. If a crystal is to be used, there are two basic low-cost types to consider: Parallel resonant AT cut quartz crystals typically ranging from 0.8 MHz to 6 MHz, and low frequency tuning fork type crystals available in several stock frequencies from 10 kHz to 240 kHz, including the popular 32.768 kHz digital watch frequency. Statek Corp., for instance, specializes in low-cost tuning fork crystals, and they have numerous free application notes to aid in design.

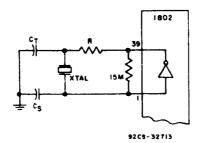

#### The Oscillator Circuit

Figure 1 shows the basic cyrstal oscillator circuit for the CDP1802. The 15 megohm resistor is used to bias the gate in its linear region so that it behaves like an amplifier. Capacitors  $C_S$  and  $C_T$  provide the required

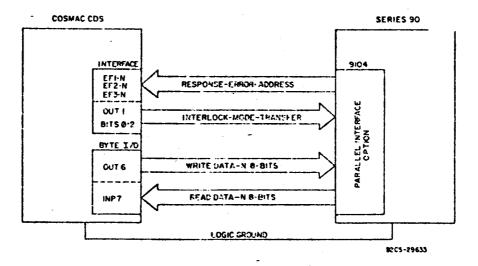

Figure 1

capacitive loading for the crystal and act as high-frequency filters to avoid overtone oscillations. The values of  $C_{\text{S}}$  and  $C_{\text{T}}$  can be calculated using the following equations found in ICAN-6086:

$$C_T = \frac{4 C_L}{1 - 5f R_e C_L}$$

, and

$$C_S = \frac{4 C_L}{3 + 5f R_e C_L}$$

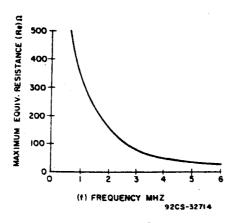

$R_{\rm e}$  is the equivalent resistance of the crystal. Figure 2 shows the approximate relation of  $R_{\rm e}$  to frequency for AT type crystals.

$C_{\rm L}$  is the load capacitance for the crystal, generally a standard value set by the crystal vendor between 10 and 32 pF.

f is the frequency in Hz.

Figure 2.

The actual value  $C_{\text{S}}$  used should be about 4 pF less than the calculated value to allow for the amplifier input capacitance.

R can usually be 0 ohms unless low power drain or stability during variable  $V_{\mbox{DD}}$  voltage is important. ICAN-6086 and ICAN-6539 explain in detail the need for and calculation of R.

#### Crystal Specifications

Frequency and Tolerance --  $\pm 0.01\%$  from -20 to  $100^{\circ}$ C is common. Tighter tolerances down to  $\pm 0.001\%$  are available at additional cost (check with vendor).

Mode of Oscillation -- Fundamental, parallel resonance.

<u>Load Capacitance</u>  $(C_L)$  -- Typically between 10 pF and 32 pF - choose a stock value the vendor has. Higher values of  $C_L$  will improve frequency stability, but lower values will decrease oscillation power consumption.

Maximum Equivalent Resistance ( $R_e$ ) -- This number is related to the frequency. Most vendors will supply crystals with  $R_e$  values lower than the curve shown in Fig. 2.

Max. Drive Level — The crystal should be able to dissipate 5 milliwatts of power. If the crystal cannot handle this level, frequency drift or even damage to the crystal may result. Crystals with lower drive capability, such as the tuning fork type, can be used if R is increased to reduce the drive level. ICAN-6086 gives details on how to compute R, also Statek has numerous free Application Notes about this.

Can Type --- HC33 and HC18 are popular types.

#### CAUTION

Don't over spec. Since virtually every parameter is a derivative of another, it is easy to specify a crystal that cannot be manufactured. It's best to work with the vendor by explaining the application.

#### Partial List of Crystal Vendors

International Crystal Mfg. 10 N. Lee Street Oklahoma City, OK 73102 405-236-3741

Statek Corp. 1200 Alvarez Ave. Orange, CA 92668 714-639-7810

#### Partial List of Ceramic Resonator Vendors

Vernitron Piezoelectric Div. 232 Forbes Road Bedford, Ohio 44146 216-232-8600

Murata Mfg. Co. Ltd. 1148 Franklin Rd. S.E. Marietta, GA. 30067 404-952-9777 Valtec Corp. 75 South Street Hopkinton, Mass. 01748 617-435-6831

M-Tron Ind. P.O. Box 630 Yankton, S.D. 57078 605-665-9321

Radio Materials Corp. 4242 W. Bryn Mawr Ave. Chicago, Ill. 60646

312-478-3600

For additional information contact Jerry Johnson - X6776.

#### Alternative Oscillator Types

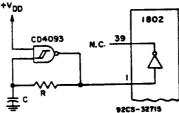

RC Type -- A simple RC oscillator is shown in Fig. 3 using a CD4093. The approximate frequency (f) is determined as follows:

$$f = \frac{1.25}{RC}$$

, at  $V_{DD} = 5V$

Unlike the CDP1802, the CDP1804 microprocessor uses a Schmitt inverter for the oscillator amplifier so that it can be used directly for the RC oscillator.

Figure 3

LC Type -- A parallel-resonant LC circuit may be used as the frequency determining network for the CDP1802. (See Fig. 4.) The frequency and component values have the following relationship:

$$f = \frac{1}{2\pi \sqrt{LC}}$$

The high-impedance secondary of a small 455 KC IF transformer similar to those found in most portable transistor radios makes an excellent LC oscillator (the C is built in). Furthermore, it is tunable (about  $\pm 10\%$ ) using the slug.

Figure 4

#### Ceramic Resonators

Made of piezo-electric material, ceramic resonators behave similar to crystals, requiring two capacitors and a bias resistor. Frequency tolerances of  $\pm 1\%$  are typical minimums. Values of  $C_1$ ,  $C_2$ , and R depend on the device used; check vendor literature.

Figure 5

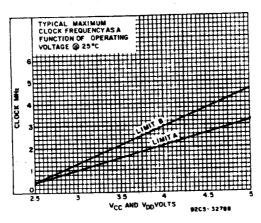

## Low Voltage Operation of the 1802

Tests indicate that a typical 1802 can operate with  $V_{CC}$  and  $V_{DD}$  as low as 2.5V, provided clock frequencies are limited to the values shown in Fig. 1 and temperature is held at 25°C. Guaranteed operation, of course, requires a custom selection.

Twenty 1802's having various date codes and package types, were tested at 25°C in a switch box without memory components. An external square wave generator was used for the clock signal, thereby eliminating crystal oscillator limitations. Details about low voltage crystal oscillator design can be found in ICAN-6539 and ICAN-6086.

Figure 1

Two instructions, SEX to F, and IRX, were loaded into the CPU by switching in the HEX codes and single stepping the clock. When running, the CPU generates addresses from 0000 to FFFF and then repeats over and over. The frequency was increased until the high address byte to TPA shift became critical. The results, shown as "limit A", indicate the frequency at which the leading edge of the high byte occurs at the trailing edge of TPA (Zero Setup Time). The November '79 Newsletter describes this phenomenon in detail.

If TPA is delayed externally to provide more set up time for the high byte, or if the high byte is not required, then the maximum frequency is merely the internal logic speed limitation of the CPU shown as "limit B".

For more information or specific applications contact Jerry Johnson, X6776.

## Data Bus Contention During CDP1802 Register-to-Register Operations

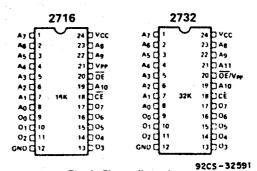

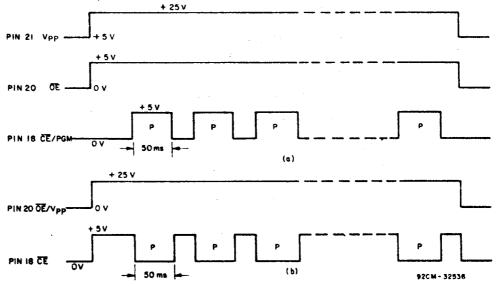

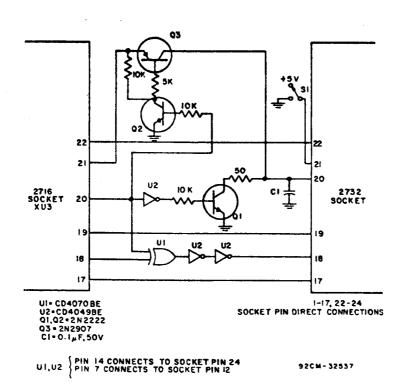

In 1802 based systems using various ROM's (CDP1832, 1834) or EPROM's (2708, 2758, 2716) bus contention problems have been found to occur during internal data transfer operations (GHI, PHI, GLO, PLO). As a result, data is lost in one or more register.

The 1802 generates a valid 16-bit address and a TPA signal during these operations. If the chip-select signals for the ROM or EPROM is only controlled by higher order address bits, then it is very probable that these memories can be selected and have their output drivers "turned on", creating a bus contention problem with the 1802 data bus drivers.

The solution to this problem is to either gate the chip-select functions with  $\overline{\text{MRD}}$  externally, or find a spare input on the memories for  $\overline{\text{MRD}}$ . During these register operations  $\overline{\text{MRD}}$  is held high. (See Table 1 on p. 90 of the MPM-201B Manual). See below for specific suggestions.

### A. Wiring MRD to a Spare Input

- CDP1834 (CS1 or CS2) only if they are "active low"

- 2716, 2732, 2758  $(\overline{OE})$

- B. Gating MRD Externally with the Chip-Select Function

For further information, contact Joe Paradise, X7352.

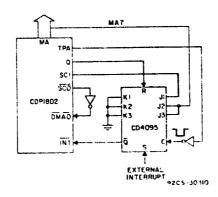

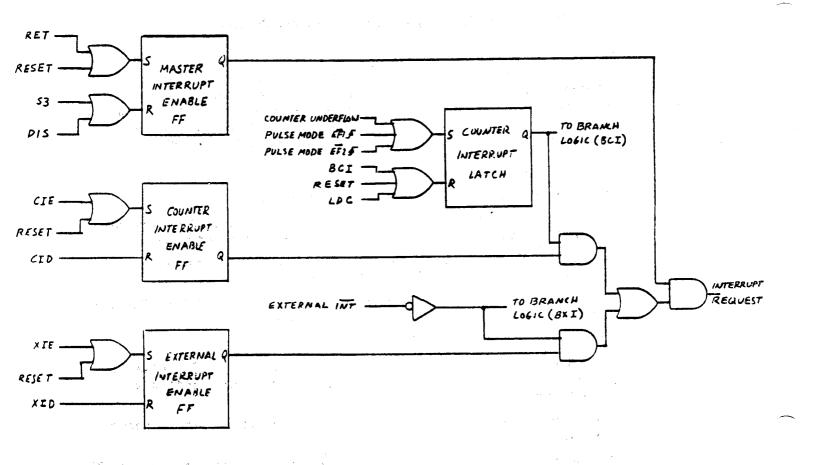

### **1802 Interrupt Control Circuits**

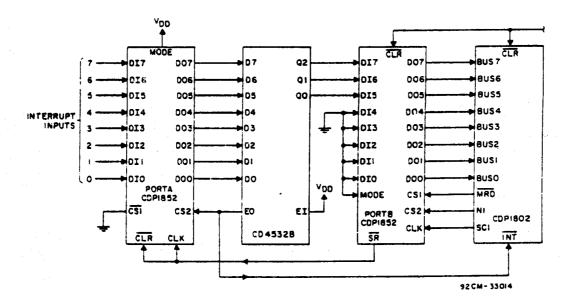

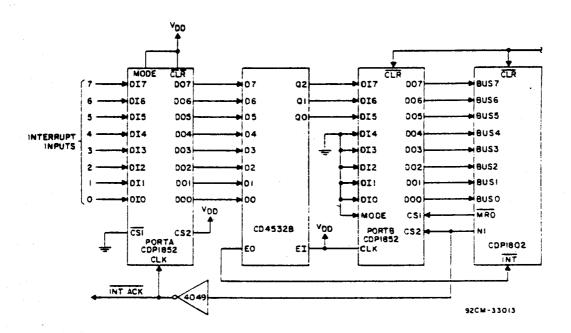

The circuits shown in Figures 1 and 2 generate a separate vectored starting address, allocating a 32 byte block of memory, for each of 8 prioritized interrupt inputs:

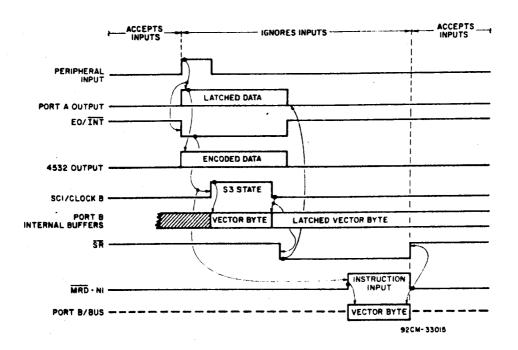

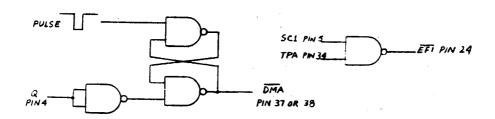

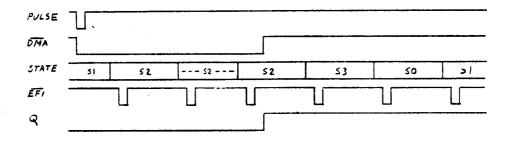

Circuit #1 - operates on a first come-first served basis, with priority arbitration for coincident input pulses. The first input pulse is asynchronously latched. Once an interrupt is initiated all inputs are ignored until the vectoring address is read by the CPU; at this time a new input may be accepted but will not be serviced until the conclusion of the existing interrupt routine. If DMA is to be used, SCO and SCI must be AND-ed together to distinguish S2 from S3 states.

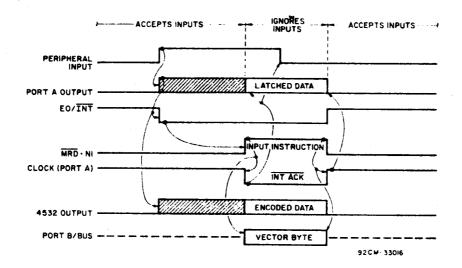

Circuit #2 - the highest priority peripheral will be serviced. Inputs are not self latching and therefore must be maintained until the CPU begins the INP instruction to read Port B. The peripheral device must remove its interrupt request before the end of the interrupt routine; peripherals could use a daisy chained interrupt acknowledge scheme.

Both circuits assume no subroutine nesting during interrupt.

| Input                         | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|-------------------------------|----|----|----|----|----|----|----|----|

| Vector<br>Address<br>Low Byte | 00 | 20 | 40 | 60 | 80 | AO | СО | EO |

For additional information contact Jerry Johnson - X6776

Figure 1

Figure 2

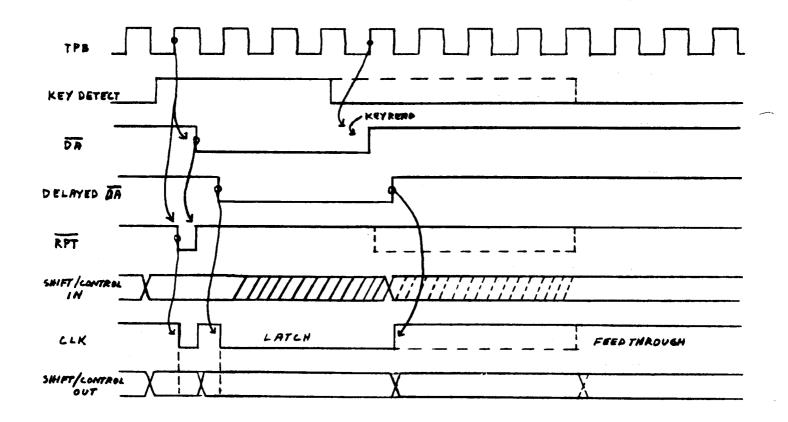

#### Timing Diagrams

Circuit #1

Circuit #2

## Using The 1802 Scratchpad To Store RAM Variables

Small systems with modest RAM requirements can sometimes be implemented without external RAM by using a portion of the 1802 scratchpad register array to store variable data. Since the scratchpad can be configured for 16-bit addresses or 8-bit data, a typical small system could allocate 8 registers for pointer addressing, and still leave 8 registers for up to 16 bytes of "RAM" storage.

A difficulty arises when attempting to perform an arithmetic or ALU operation on register data: these operations require M(R(X)) and the D register as operands. Register to D manipulations can be performed with PHI, GHI, PLO, and GLO instructions, but R(X) cannot point to an internal register to complete the operation.

The problem can be solved if one page of ROM is available for use as a lookup table. With this method, one register operand becomes the lower order table pointer address, while the other operand is transferred to D. The lookup table contains sequential bytes from 00 to FF, and when the arithmetic or ALU operation is performed, the table contents and D are operated upon, with the result in the D register.

#### EXAMPLE

- o Register data is stored in R(9).1 and R(B).0

- o An XOR instruction is to be performed  $[M(R(X)) \oplus D \longrightarrow \overline{D}]$

- o Lookup table is located in locations Ø3ØØ Ø3FF

- o R(7) is dedicated as lookup table pointer

- o R(7).1 has already been initialized to Ø3

#### MACRO:

GHI R9 . . . Get first operand into D

PLO R7 . . . Use first operand to lookup table value

GLO RB . . . Get second operand into D

XOR . . . Exclusive-OR D with contents of table address

if R(9).1 = AA and R(B).0 = FF

then R(7) would point to address #3AA

Contents of Ø3AA = AA

$M(R(X)) \oplus D = AA \oplus FF = 55$

D will contain 55 when operation is complete

The idea for this article was submitted by John Stahler, RCA, Des Plaines.

For information on related topics, contact Joe Paradise, X7352.

# Microprocessors Application Note ICAN-6704

# Optimizing Hardware/Software Trade-Offs In RCA CDP1802 Microprocessor Applications

By L.A. Solomon and D. Block

One of the chief reasons for choosing to design with a microprocessor rather than standard IC's is to reduce a system's parts count. To make the best choice requires a careful analysis of hardware/software trade-offs. This analysis usually narrows down to the ratio of ROM to I/O devices in the system. Economics indicates that the more functions handled in software. the less expensive and more flexible the system will be. Thus, a good design practice is to attempt to do everything in software initially and then relegate functions to hardware only as the speed/processing capability of the CPU becomes taxed. This Note will develop some examples of processor interfaces that not only minimize external hardware but, through judicious programming techniques, also minimize speed requirements on the CPU.

The RCA CDP1802 microprocessor is particularly well suited to minimum-cost interfacing because it has a significant number of terminal connections dedicated to I/O operations and an extensive set of I/O instructions. It has three I/O selection lines, called the "N" lines, that are controlled by I/O instructions plus four general-purpose flag input lines testable with branch instructions. There also DMA-in, DMA-out, Interrupt Request line inputs as well as two state code and two timing pulse outputs to synchronize I/O devices to the CPU. A single bit output (Q) which can be set or resct under program control is also provided. In all, 15 of the CDP1802 terminal connections are dedicated exclusively to I/O control. In addition, the CDP1802 has other unique architectural features, such as built-in DMA, that can be used to advantage. These features will also be discussed.

#### A CLASSICAL SYSTEM

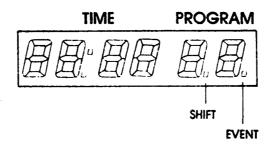

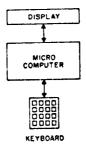

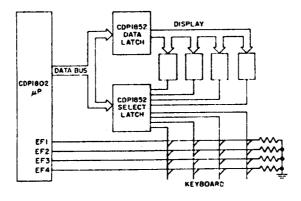

A simple system having a keyboard input and a digital display output is shown in Fig. 1. The specific functions are

9205-29670

Fig. 1 - Simple microcomputer system.

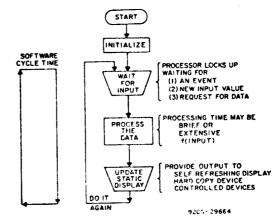

omitted because the immediate concerns are only the microprocessor and I/O interfaces. These interfaces will be constrained by the programming technique choosen for the system. In the classical software control flowchart for this system, shown in Fig. 2, the standard

Fig. 2 - Classical software control flowchart for the system of Fig. 1.

initialization block is followed by an input, processing, and output procedure with a final loop back to repeat the action. Even without the details of the hardware or software design or the specific application, certain predictions can be made about this system.

First, consider the software cycle time, that is the time to go completely through one loop of the procedure. The cycle time is the sum of the time spent in each portion including input, of the software. processing, and output. Because the program apparently waits for an input, the time spent in the input block is indeterminate. The system cycle time, indeterminate. therefore, is parameter has immediate impact on the selection of both input and output devices used in the system. The output device, for instance, must be capable of operating for prolonged periods without processor attention. Therefore, it must be a device that is self-refreshing or contains a latch. It certainly cannot be dynamic because no provision for refreshing is apparent in the simple software structure shown thus far. Because dynamically refreshed displays have the potential for lower cost, the static requirement is a serious drawback.

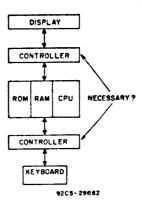

Next, consider an input device. A keyboard, being human operated, will present data to the processor at an uneven rate. The time between keystrokes may vary from a few milliseconds to several seconds or minutes. With the flowchart given, the processor must complete its processing before the next input can be received. If each keystroke requires some analysis by the microprocessor, a choice between using a very fast (and expensive) processor or lengthening the minimum time between keystrokes must be made. The first alternative would be very wasteful since the processor's very fast speed would only be needed in short bursts; most of the time it would be idling waiting for an input. The second alternative leads to an unresponsive system, one in which the operator will have to adjust to the system rather than the other way around. A third alternative is to design in an "intelligent" keyboard controller or buffering device to smooth out the input rate as depicted in Fig. 3. This alternative, however, is not ideal either because it requires additional hardware expense.

Resorting to additional hardware, however, may not be necessary if the flowchart of Fig. 3 is restructured. By doing the controller functions in the

Fig. 3 - Addition of controllers to smooth out input rate.

software the controllers can be eliminated at only the cost of enlarging the system ROM. Moreover, because ROM's come in fixed increments, it may be no more expensive to have a program that is 1024 bytes long than one that is 527 bytes, even though one is nearly twice as long as the other. In fact, if there is unused space in the system ROM, the controller function may be had for "free". Even if an additional ROM is required, it may cost less than the MSI or LSI controller being replaced.

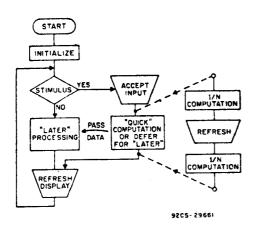

To take advantage of software control, the approach is changed, so that instead of waiting for an input to take place, the system simply looks at the input periodically. If no input is present, it skips the input operation and goes on to something else. That something else could be the refreshing of a dynamic display, for example, or some processing required as the result of the last input. If an input is present, then it is accepted and acted on. There are several options available for handling the processing associated with this input. If the input is small and can be handled immediately, the system will do so. If not, it can be saved for later when there will be time to handle it, or it can be broken up into small computational blocks interspersed among other tasks such as display refresh. These approaches are flowcharted in Fig. 4. The latter approach is the idea behind a powerful technique called interpretive programming in which functions such as display refresh and keyboard scan are written as modular subroutines. Calls to these subroutines, which pass or pick up parameters from the main program, can be interspersed throughout the main program wherever required by the system timing considerations.

Fig. 4 - Controller function transferred to software and input loads interspersed.

#### HANDLING A DYNAMIC DISPLAY

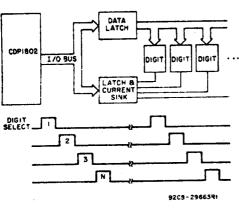

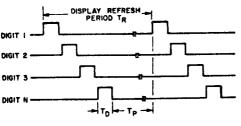

Fig. 5 shows a typical multiplexed display system and Fig. 6 gives the details on the display refresh rate. The minimum refresh rate for any digit should be 100 Hz, which is fast enough to prevent flicker under most stationary display conditions.

Fig. 5 - Typical multiplexed display system.

- . DISPLAY REFRESH RATE > 100 Hz

- MINIMIZING N·TD WILL MAXIMIZE TP

- . TP IS THE AVAILABLE PROCESSING TIME

92 05 - 29664

Fig. 6 - Details of the display refresh rate.

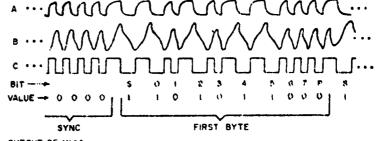

The actual ON time (T<sub>D</sub>) of any digit is a trade-off between the intensity of the display and the time remaining within the 100-Hz refresh period for the processor to do some other work. It is desirable to minimize T<sub>D</sub> so that a maximum of processing time (T<sub>D</sub>) is left for the rest of the processing load.

It is customary to "overdrive" multiplexed LED displays to increase their apparent brightness. The extent to which overdrive is practical is a function of the duty cycle

$$\frac{T_{\mathrm{D}}}{T_{\mathrm{R}}}$$

of the display. This technique, however, is not without risk. Should the program crash or hang up (because of a program bug or noise injected into the system, or component failure, etc.), it is quite probable that a digit driver will be incinerated. Because of this hazard appropriate precautions, particularly when debugging a system, should be taken.

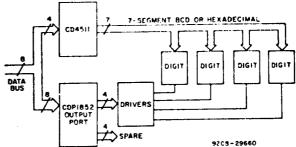

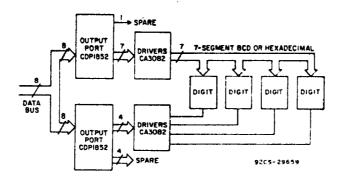

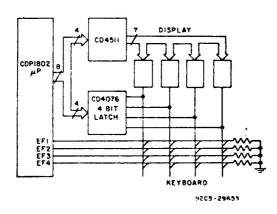

The segment information for a 7-segment display can be handled in either of two ways. If the data is in BCD, a device such as the CD4511 which contains a latch, BCD-to-7-segment decoder, and drivers can be used as shown in Fig. 7. Or,

Fig. 7 - Handling segment information in hardware by means of a CD4511 BCD-to-7-segment latch decoder driver.

instead of the CD4511 that does code conversion in hardware, a software conversion via a look-up table can be used along with a simple output port as shown in Fig. 8. Hexadecimal or other codes are also easily accommodated in the table look-up method. But, because the output ports may not have sufficient drive to directly handle LED's, an intermediate stage of buffering may be necessary. No clear-cut recommendation can be made because variables such as the number of devices and the type of display chosen are significant.

Fig. 8 - Handling segment information in software by means of an output port and lookup table.

#### SINGLE-SIGNAL INPUTS

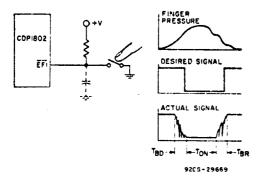

The CDP1802 has four flag input lines that can be tested with branch instructions. These inputs are general purpose and can be used for such functions as interrupt vectoring, status indicators, or as single-bit inputs for slowly varying signals such as that of an ASCII terminal having a moderate baud rate. As an example, one of the flag lines is used as an input for a switch in Fig. 9. To signal

Fig. 9 - Basic switch circuit using microprocessor flag line.

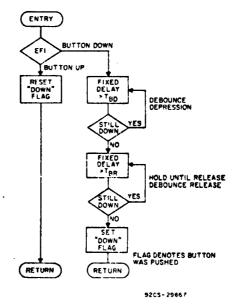

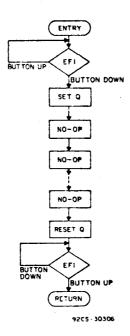

the processor, a change on the flag line from a logic 1 to logic 0 level is used. However, the tendency of mechanical switches to "bounce" prevents this simplistic solution. The actual signal presented to the microprocessor consists of three parts - an initial bounce, a stable ON period, and a release bounce. A program looking only for a simple 1 to 0 to 1 transition may sense many switch closures because of the bounce noise. Although there are hardware solutions to this problem, software techniques may prove more cost-effective. Fig. 10 is a flowchart of a subroutine to debounce a mechanical switch. A test is made on the input signal to test for a switch closure. If none is found, a "switch down" software flag is

Fig. 10 - Flowchart of subroutine for debouncing a mechanical switch.

reset. This flag may be some convenient bit in one of the CDP1802's sixteen general purpose CPU registers or a bit in a RAM status word. If the switch is down. then the software will loop, waiting for the button to be released. The wait is performed to insure that the switch is not "seen" again for the current depression and to allow for the initial bounce period TBD. Once the switch is released, the switch is again interrogated until it reaches a stable OFF condition. The software flag indicating a "switch down" condition is set, and the program returns to the caller. Although this program is easy to understand, it is, like the earlier simple solutions, not without its problems. For instance, the processor again wastes valuable time. The execution time (see Fig. 9) for this subroutine is at least

$$T_{BD} + T_{BR}$$

and does, in fact, last as long as the button is depressed. Thus, it is obviously not suitable for systems having dynamically refreshed displays. A further drawback, from the human-engineering standpoint, is that a response is made on the release of the switch rather than on its depression, the opposite of what one would normally expect.

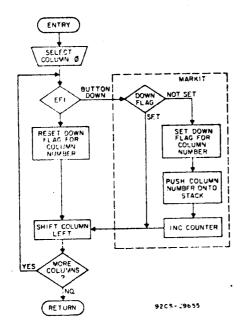

Fig. 11 shows a flowchart for an im-

Fig. 11 - Flowchart of improved subroutine for debouncing a mechanical switch.

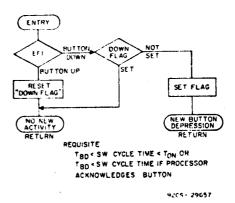

proved method that overcomes both of these drawbacks. Here, the subroutine that looks at the input signal has the capability of remembering what that signal was the last time it looked. This information is saved in a software flag called the "down flag". The routine operates as follows. If the button is now down and was also down the last time, then it is assumed that the system sees the same button depression seen earlier. A return is made to the caller with an indication of no new activity. If the button is not now down, but was the last time, then the switch has been released. In this case, the "down flag" is reset and a return made to the caller indicating no new activity lit is assumed that the processor is interested only in switch depressions and not their duration). But, if the switch is down now and was not down the last time, then there is a new depression. The switch must be debounced, the "down flag" set, and a message returned to the caller. Notice in the flowchart that a second test was made after the delay generated in the "busy work" block. This delayed second test is a debouncing technique to determine that the switch has been in the same state for two successive samplings before a decision is made on the true state of the switch. This method is still not optimal because the program is waiting (and therefore wasting time) during the debounce period. If some additional constraints are placed on the software cycle time, however, the program can be further optimized. For example, if the cycle time is greater than the bounce time (TBD) but less than the switch ON time (TON), then the flowchart can be simplified to Fig. 12. Here there are no timewasting loops because switch bounce, in effect, will not be seen within the given timing restraints.

Fig. 12 - Flowchart of simplified debouncing subroutine benefitting from additional constraints.

#### MULTIPLE INPUTS

Up to four inputs can be handled as described above with each switch connected to a separate flag line of the CDP1802. Another technique is a multiplexing scheme in which the four switches are connected to one flag input, as shown in Fig. 13, and sequentially scanned as described in the flowchart of Fig. 14. This technique is readily expandable to additional scanned functions and, therefore, is discussed in detail. The

Fig. 13 - Hardware for handling four switch inputs on one flag line by means of a scanning routine.

Fig. 14 - Flowchart of scanning routine for handling four switch inputs.

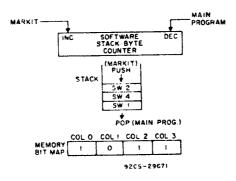

subroutine is designed to look for new switch closures and report them to the main program by "pushing" the switch number of a newly closed switch onto a stack and incrementing a counter. The main program will "pop" switch numbers off the stack and decrement the counter whenever the count is greater than zero. In the CDP1802 any one of the 16 general-purpose registers can be conveniently used as a counter because each has its own increment and decrement instruction.

The auxiliary functions for the subroutine are shown in Fig. 15. It is

Fig. 15 - Auxillary functions for the scanning subroutine of Fig. 14.

assumed that the timing constraints of Fig. 12 are met by this routine also, so that Fig. 14 is an extension of the basic flowchart previously developed. Upon entry into the subroutine, the first switch column is selected by outputting a 1 in bit position 0 of the data bus and examining the switch associated with that position. If

a new depression is detected, the "down flag" is set for that switch in the memory bit map, the column number is pushed onto the stack, and the counter ineremented. Next, the column is shifted and, if more columns remain to be scanned, the process is repeated. No switch closure or no new switch closure simply results in a column shift and continuation. When all columns have been scanned, a return to the main program is executed. The main program detects if any new switch closures have occurred by seeing if the counter has a value greater than zero. If so, the main program successively "pops" a switch number from the stack and decrements the counter until it reaches zero.

A section of the flowchart in Fig. 14 has been partitioned off and labeled "MARKIT". This routine is a common one that can be used as an expanded keyboard scan rountine discussed in the next section. It should be noted that the approach taken above lends itself well to a multi-processor system in which one processor handles the keyboard scanning and puts key numbers in a stack accessible to the other processors as well.

#### KEYBOARD SCANNING TECHNIQUES

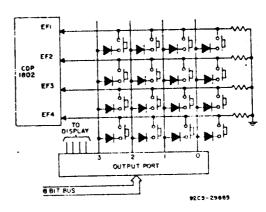

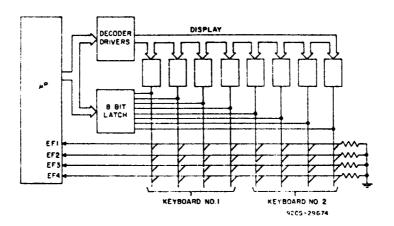

Fig. 16 shows an arrangement for

Fig. 16 - Hardware arrangement for handling a 16-key matrix using a scanning routine.

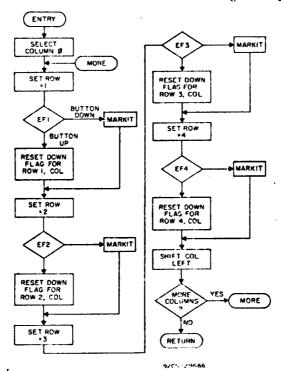

scanning a 16-key matrix. It is a simple extension of the arrangement just discussed. The horizontal lines can go directly into the four flag inputs of the CDP1802 as shown. Fig. 17 gives a flowchart of the software in which "MARKIT" is now responsible for handling row as well as column information. The basic interface between

the main program and the keyboard scan subroutine remains the same; the subroutine place new key depressions on the stack and from there they are passed to the main program. Note that a key number's position on the stack does not necessarily represent when a given key was depressed with respect to the other keys on the stack, but merely indicates the order in which the keys were scanned. Because the stack is emptied on each cycle by the main program and only new key depressions are entered, the presence of two key numbers on the stack tells only that both keys were down when the scan took place. To discriminate in time between rapid key depressions, a short software cycle time is necessary. But, remember that this time must be kept within the constraints of TpR, TpD, and ToN. There is a limitation to the technique discussed in that the software does not indicate to the main program when a key has been released. Thus, it can not be used in a system requiring lockout of other keys when any one key is down.

## COMBINED DISPLAY AND KEYBOARD

The whole system of Fig. 1 is shown with its component blocks filled in on Fig. 18. The original objective to minimize

Fig. 17 - Flow chart of software for handling row and column information utilizing "MARKIT" routine.

Fig. 18 - Simple microcomputer system of Fig. 1 with component blocks expanded.

hardware has been realized in that only two 8-bit output ports are required in this design besides digit drivers (not shown).

A further improvement can be made in the system by combining the keyboard scan and display multiplexing signals as shown in Fig. 19. Here, a single-byte

Fig. 19 - System Improvement made by combining keyboard scan and display multiplexing signals.

output is used with the upper-order 4-bits being BCD data for the display and the lower-order 4 bits used to simultaneously select a display digit and keyboard column. This arrangement does not reduce the parts count, but does give smaller packages if space is a consideration and cuts down on the number of output operations and output bytes stored. A ready expansion of the system shown in Fig. 20 still uses only two IC's but permits scanning two 16-key keyboards and an 8-digit display.

#### TIMING GENERATION

In many applications it may be necessary to have some time-keeping ability in the microprocessor system. The requirements may range from having a time-of-day or elapsed-time clock to microsecond timing resolution for generating precision pulse widths. Here again, of the many approaches possible to timekeeping, a cost/performance-optimized one can be found.

Consider an example, shown in Fig. 21, for generating an output pulse of width  $T_1$  each time switch  $S_1$  is closed. The CD-

Fig. 21 · System for generating an output pulse for each switch closure.

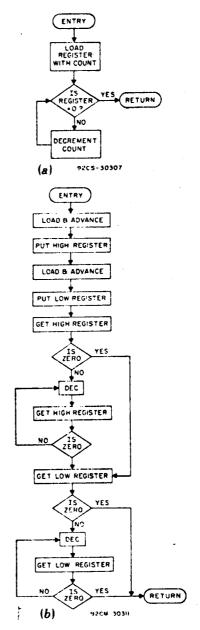

P1802 has a single-bit output called the Q flip-flop that can be set or reset under program control to perform this function. The simplest technique for generating a fixed delay is by executing a series of "noops" in the program as illustrated in Fig. 22. If each "no-op" takes 5 microseconds to execute, for example, and T<sub>1</sub> is 50 microseconds long, then ten "no-ops" would do the job. This technique is obviously not a realistic one for long timing intervals because it is extremely wasteful of memory and fully occupies the processor with a non-productive task.

Fig. 20 - An expanded system with 8-digit display and two 16-key keyboards.

Fig. 22 - Primitive programming technique for pulse generation.

A better technique is shown in Fig. 23(a). Here a counter is preset with a given value and continually decremented until it reaches zero. In the CDP1802 one of the 16-bit general-purpose registers can be used for this function. Fig. 23(b) shows the specific instruction sequence. This technique saves a lot of memory bytes but still ties up the processor. For maximum processor efficiency it would be best to load an external counter that would count at some preset rate and generate an interrupt to the processor when it reaches zero. Meanwhile, the processor could be doing some useful work. Such a system is shown in Fig. 24, but it does not minimize system hardware.

Fig. 23 - (a) Basic flowchart of improved technique for pulse generation. (b) Specific instruction sequence for improved pulsegeneration technique.

Fig. 24 - System for puise generation using an external counter.

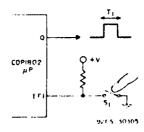

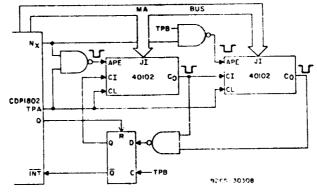

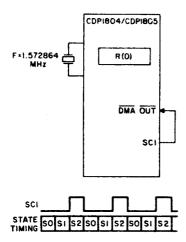

An interval timer can readily be made for the CDP 1802 with no external parts by making use of an internal register that can be automatically incremented. Generalpurpose register R0 is used as a pointer for DMA operations in the CDP1802 and, as such, is automatically incremented on each DMA (in or out) cycle. By connecting the State Code 1 (SC1) line output back to the DMA Out request line (DMAO), the CDP1802 performs one DMA cycle for each Fetch and Execute cycle, as shown in Fig. 25, thereby providing a built-in timer and instruction counter. With a clock frequency of 1.57 MHz, the most significant bit of R0 will change each 1/2 second, providing a realtime clock. CPU operation is, of course, slowed by 1/3 with this scheme, but with an upper clock frequency of 6.4 MHz the system can be made fast enough for many applications.

With the circuitry of Fig. 26, a general-purpose interval timer can be realized. This circuit will cause an interrupt when the most significant bit of register R0 goes to a "one". Thus by preloading R0 with a desired count, a timing interval with a range of 215 and a resolution of up to 3.75 microseconds (with a clock frequency of 6.4 MHz) can be obtained with a minimum of external hardware and yet leave the processor free to do useful work.

#### ACKNOWLEDGMENT

The authors wish to acknowledge the contributions of Messrs. K. Karstad and F. Thorley for developing some of the techniques described.

Fig. 25 - Use of DMA-Out line to implement an Internal timer.

Fig. 26 - Use of Interrupt line to implement a general-purpose timer.

When incorporating RCA Solid State Devices in equipment, it is recommended that the designer refer to "Operating Considerations for RCA Solid State Devices", Form No. 1CE-402, available on request from RCA Solid State Division, Box 3200, Somerville, N. J. 98876.

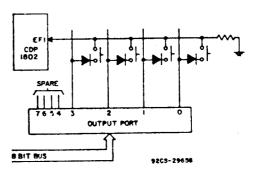

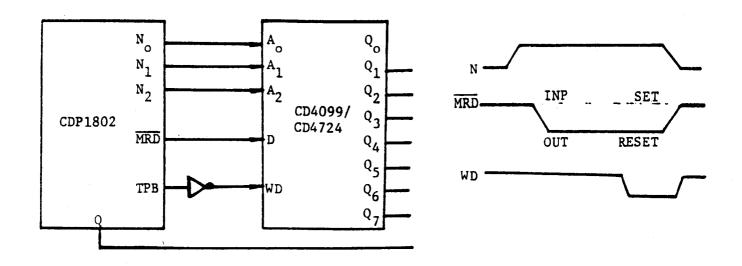

## CDP1802 Expanded Output Control Using the CD4099

For simple I/O control applications, the only available 1802 output control line with latched set and reset capability is the Q output, controlled with a single SEQ or REQ software instruction. With the addition of a CMOS CD4099/CD4724 and a single inverter, a comparable single instruction can expand this capability to 8 outputs.

Conventional I/O control usually involves an I/O port, which latches control data from the data bus line. The primary disadvantage is that several instruction bytes (and instruction cycles) are required to modify a single control bit based on a conditional computed result. Besides the disadvantage of additional ROM code, the response time of a peripheral device to a CPU command is delayed by the time it takes to execute this instruction sequence.

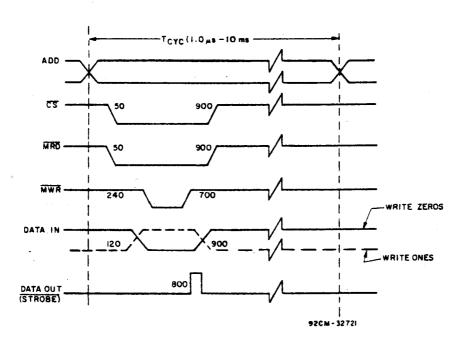

The circuit and waveforms of Figures 1 and 2 illustrate the implementation of a CD4099/CD4724 as an alternate means of expanding I/O control. The CD4099/CD4724 is an inexpensive addressable latch in a 16 lead package that can use the N lines to select an internal latch for modification. Depending on the level of the data input at the time WD is low, the selected output can be set or reset without modifying any previous condition on the other outputs. This can be easily accomplished with the I/O instructions on the 1802, which can generate 7 combinations of N line codes, with MRD high for an INP instruction, and low for an OUT instruction. These combinations result in the table of single instructions shown in Table 1 that can selectively set or reset individual control bits in the expanded 1802 system.

Fig. 1 - CD4099/CD4724 Hardware Implementation

Fig. 2 - Timing Diagram

TABLE I - Single Bit Output Control Codes

|                                                                      | Set With |         | Res      | et With |

|----------------------------------------------------------------------|----------|---------|----------|---------|

| Output                                                               |          | Machine |          | Machine |

| Pin                                                                  | Mnemonic | Code    | Mnemonic | Code    |

| $Q_1$                                                                | INP 1    | 69      | OUT 1    | 61.     |

| Q <sub>1</sub> Q <sub>2</sub>                                        | INP 2    | 6A      | OUT 2    | 62      |

| Q <sub>3</sub>                                                       | INP 3    | 6B      | our 3    | 63      |

| Q <sub>3</sub><br>Q <sub>4</sub><br>Q <sub>5</sub><br>Q <sub>6</sub> | INP 4    | 6C      | OUT 4    | 64      |

| Q <sub>5</sub>                                                       | INP 5    | 6D      | out 5    | 65      |

| Q <sub>6</sub>                                                       | INP 6    | 6E      | out 6    | 66      |

| Q <sub>7</sub>                                                       | INP 7    | 6F      | OUT 7    | 67      |

| . Q                                                                  | SEQ      | 7B      | REQ      | 7A      |

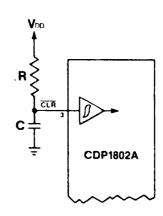

## CDP1802 Versus CDP1802A - Performance Enhancements

In the past, latching of the high-order address byte determined system speed for most 1802 based designs. The original CDP1802 CPU had a high byte set up before TPA trailing edge time (Tsu) which would diminish to zero at a clock speed of 2.5 MHz (see Fig. 1), thrus limiting system performance to 2.5 MHz maximum.

The new CDP1802A CPU has modified internal logic and art work changes, which reduce the memory address propagation delay, and provide a more generous set up time (Tsu) than its predecessor. The maximum clock frequency is no longer limited by Tsu, but depends entirely on internal logic speed limitations. Operation

at 5V, 3.2 MHz, from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  is guaranteed, with a minimum Tsu of 75 nsec. (See Fig. 1).

Another design improvement is the addition of an internal Schmitt Trigger buffer to the CLEAR input, eliminating the need for external logic devices for power on reset. The internal Schmitt input provides a hysteresis voltage of approximately 1/2 volt, so that the RC network may be connected directly to pin 3 as shown in Fig. 2.

The CDP1802A CPU is pin for pin compatible and functionally equivalent to the older CDP1802 CPU, and will perform in any existing 1802 based designs.

Minimum High-Order-Memory-Address Byte setup to TPA time. Tsu T4 = - 40 to + 85 °C 600 400 CDP1802A 300 200 150 100 CDP1802 80 50 40 30 Clock frequency MHz

Figure 2:

# Microprocessor Products Application Note ICAN-6842

## 16-Bit Operations in the CDP1802 Microprocessor

by D. Block

Although the CDP1802 microprocessor is an 8-bit machine, it contains mostly 16-bit registers. Its sixteen 16-bit registers are all general-purpose types, giving the CDP1802 a great deal of flexibility and the flavor of a 16-bit microprocessor in many respects. This paper describes various software routines and a few interface circuits that can be used to manipulate full 16-bit values in the CDP1802.

The areas of logical, shift, and arithmetic operations are all considered along with I/O and loop counters. In sophisticated systems where multiplications and/or divisions are required, a hardware approach using the CDP1855 Multiply/Divide unit should be investigated. These 8-bit units can be cascaded, so that up to 32-bit operations can be performed. For simpler systems, the software approach described below is probably the best choice.

#### General

In many of the following examples, a 16-bit data word will be located in memory. Since the CDP1802 is an 8-bit machine, of necessity the word will have to be stored as two 8-bit bytes. As a convention, assume that the 16-bit word is located in two consecutive locations with the most significant byte occupying the higher address.

#### **Logic Operations**

The logic operations provided by the CDP1802 are AND, OR, and EXCLUSIVE OR. These three operations are normally performed between an operand in the D register and a byte from memory. With the addition of a few instructions, register-to-register operations can also be accomplished, as shown in Example 2, below.

#### Example 1: Register/Memory Operations

In this example, a 16-bit OR is performed between the contents of an R register called REG1 and two bytes of memory pointed to by another register called POINTR. The results will be in REG1.

| SEX POINTR                 | POINT X TO FIRST<br>(LOWEST)<br>MEMORY BYTE |

|----------------------------|---------------------------------------------|

| GLO REG1<br>OR<br>PLO REG1 | OR LOW BYTES                                |

| INC POINTR                 | POINT TO<br>HIGHEST<br>MEMORY BYTE          |

| GHI REG1<br>OR<br>PHI REG1 | OR HI BYTES<br>RESTORE<br>RESULTS           |

|                            |                                             |

## Example 2: Register-to-Register Operations

If the two operands are in two registers called REG1 and REG2, the code below can be used; it is only three bytes longer than that of example 1. Here, again, the results will be returned to REG1.

| SEX POINTR | SET A POINTER<br>TO A FREE BYTE |

|------------|---------------------------------|

| GLO REG1   |                                 |

| STR POINTR | STORE LOW BYTE                  |

|            | OF REG1                         |

| GLO REG2   |                                 |

| OR         | OR LOW BYTES                    |

| PLO REG1   | RESULTS                         |

|            | RETURNED TO                     |

|            | REG1                            |

| GHI REG1   |                                 |

| STR POINTR | STORE HI BYTE                   |

|            | OF REG1                         |

| GHI REG2   |                                 |

| OR         | OR HI BYTES                     |

| PHI REG1   | RESULTS TO REG1                 |

|            |                                 |

#### Shift Operations

In the CDP1802, shifts are performed on the contents of the D-register in either circular shifts, with data bits circulating through DF, or open shifts, in which zeros are shifted into one end of the D-register. Either type of operation can be performed on the full 16 bits of an R-register, as shown below. Right shifts are performed by substituting the appropriate shift-right commands for the shift-left commands given in the examples.

#### Example 3: Shift Left (Open)

| GLO REG1 | GET LOW BYTE                              |

|----------|-------------------------------------------|

| SHL      | SHIFT LEFT                                |

| PLO REG1 | RESTORE                                   |

| GHI REG1 | GET HI BYTE                               |

| SHLC     | SHIFT LEFT WITH<br>CARRY BRINGS IN<br>LSB |

| PHI REG1 | RESTORE                                   |

#### Example 4: Shift Left Circular

| GLO REG1 |                 |

|----------|-----------------|

| SHL      | SET UP CARRY    |

|          | INTO HI BYTE    |

| GHI REG1 |                 |

| SHLC     | SHIFT IN CARRY  |

| PHI REG1 | CARRY INTO LOW  |

|          | BYTE LEFT IN DF |

| GLO REG1 |                 |

| SHLC     | SHIFT CARRY     |

|          | INTO LOW BYTE   |

| PLO REG1 |                 |

A 16-bit shift of two consecutive memory bytes is performed similarly by replacing the GET and PUT statement by memory reference commands as follows:

#### **Example 5: Shift Left-Memory Location**

| то |

|----|

|    |

|    |

|    |

|    |

|    |

|    |

|    |

## Example 6: Shift Left Circular — Memory Locations

LDA REG1 SHL LDN REG1 SHLC STR REG1 DEC REG1 LDN REG1 SHLC STR REG1

#### **Arithmetic Operations**

Sixteen-bit arithmetic is straightforward in the CDP1802 since arithmetic operations including the value of the DF flag are included in the instruction set. Arithmetic operations are performed between a byte in the D-register and a byte from memory but, again, the addition of a

few extra instructions makes register-toregister operations possible.

DOINT TO

#### **Example 7: Register/Memory Addition**

CEY DOINTD

| SEX POINTR | MEMORY        |

|------------|---------------|

|            | LOW BYTE      |

|            | OPERAND       |

| GLO REG1   |               |

| ADD        |               |

| PLO REG1   | RESULTS       |

|            | RESTORED TO   |

|            | REG1          |

| IRX        | POINT TO HIGH |

|            | BYTE          |

| GHI REG1   |               |

| ADC        |               |

| PHI REG1   |               |

#### Example 8: Register/Register Addition

| SEX POINTR                   | STORE REG2 HI<br>BYTE              |

|------------------------------|------------------------------------|

| GHI REG2<br>STXD<br>GLO REG2 | 07005 D500 L0W                     |

| STR POINTR                   | STORE REG2 LOW<br>BYTE             |

| GLO REG1                     | SAME AS PREVIOUS EXAMPLE FROM HERE |

| ADD<br>PHI REG1              |                                    |

|                              |                                    |

PHI REG1 IRX GHI REG1 ADC PHI REG1

Note that if each byte had been operated on in sequence, as was done in Example 2, rather than storing both haives of REG2 and then operating on them, the code could have been reduced by one instruction. This reduction could be significant in some applications.

#### Counters

An increment or decrement instruction to an R-register operates on the full 16 bits of the register. Thus, loop counters of up to 65k counts are readily available. The most direct implementation of a loop counter involves the presetting of an R-register with the desired number, decrementing it once each time through the loop, and testing for zero in the counter. The following example sets up a loop counter for 512 counts.

#### Example 9: Output 512 Bytes

LDI #02; PHI COUNTR

..SET COUNTER =

#0200

LDI #00; PLO COUNTR

LOOP: OUT1 ..DO

..DO AN OUTPUT OPERATION

**DEC COUNTR**

..DECREMENT THE

COUNT

**GLO COUNTR**

..CHECK LOW HALF OF

COUNTER

BNZ LOOP

**GHI COUNTR**

..CHECK HI HALF OF COUNTER

**BNZ LOOP**

XX

..NEXT INSTRUC-TION AFTER LOOP

Note that an output instruction outputs MR(X) and then increments R(X), so that this example would output 512 consecutive bytes from memory. Of course, for smaller loops of less than 256 counts, only the low half of a register need be examined, and two instructions can be removed from the loop.

Care must be exercised, when designing timing loops, to equalize the various branch path lengths. The method shown in example 9 would not be suitable for real-time loops. Instead, a loop of the form shown in example 10 should be used.

#### **Example 10: Timing Loop**

LDI #20; PHI TIMER

.. SET COUNT

LDI #00; PLO TIMER

LOOP: DEC TIMER

..DECREMENT

TIMER

**GLO TIMER**

BZ ENDTST

..TEST LOW BYTE

GLO TIMER ...DUMMY, IN-

STRUCTION TO

MATCH DELAYS

BR LOOP

ENDTST: GHI

TIMER BNZ LOOP ..TEST HI BYTE

XX

..NEXT IN-STRUCTION

Two notes of caution should be mentioned here. First, a short branch instruction takes two machine cycles, whereas a long branch requires three -- avoid mixing them in a loop. In particular beware of the trap caused by editing long branches into a file in response to assembler-generated "branch out of page" errors. Make sure first that these branches are not in a timing loop. Second, beware of inserting NOP instructions to match delays, as these are three-machine-cycle instructions

## A Hardware Approach to Timing Generation

A general-purpose time-delay subroutine can be devised which takes a

passed parameter, puts its value into a register, counts it down to zero, and returns to the caller. Significant time delays can be generated by this method when a 16-bit value is passed, as shown below.

## Example 11: General-Purpose Time Delay Subroutine

The main program, using the Standard Call and Return Technique, would look like this when #OFFF is the value being passed:

SEP R4, A(DELAY), #OFFF

#### The Subroutine itself follows:

**DELAY:LDA R6**

PHI TIMER ..LOAD PASSED

**PARAMETER**

LDA R6; PLO TIMER

SKP ...THIS ENABLES

ZERO TO BE PASSES

LOOP: DEC TIMER

..DECREMENT ..TEST LOW BYTE

GLO TIMER

BZ ENDTST

GLO TIMER ...DU

..DUMMY INST TO

MATCH DELAYS

BR LOOP

**ENDTST: GHI TIMER**

..TEST HI BYTE

**BNZ LOOP**

SEP R5

..RETURN-WHEN

ZERO REACHED

A method of creating an on-board time in the CDP1802 by using its built-in DMA facilities is described in Reference 1.

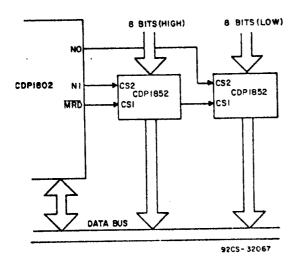

#### Input/Output

Inputting a 16-bit word to one of the R registers is a trivial matter in both hardware and software. Fig. 1 shows two input ports where N0 and N1 have been used to select the low and high bytes, respectively, of a 16-bit word. The code required to load this word into REG1 appears below:

## Example 11: Input a 16-Bit Word to a Register

INP1 ..BRING LOW BYTE

INTO D

PLO REG1 ..TRANSFER IT TO

LOW HALF OF

REG1

INP2 ...BRING IN HI BYTE

PHI REG1 ..STORE IT

A shorter software sequence can be developed to input the word into two con-

Fig. 1-Basic 16-bit Input circult.

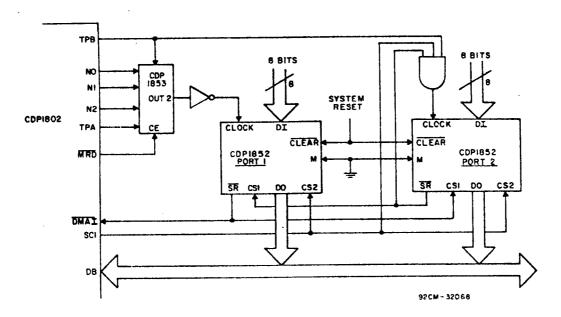

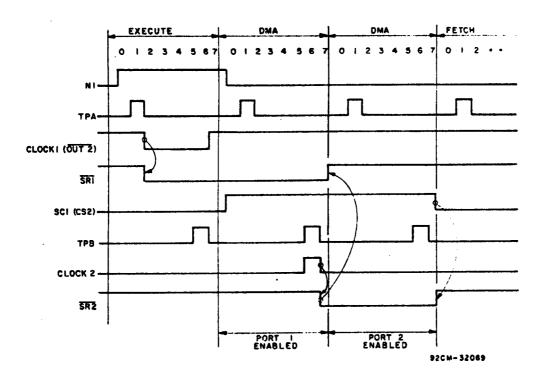

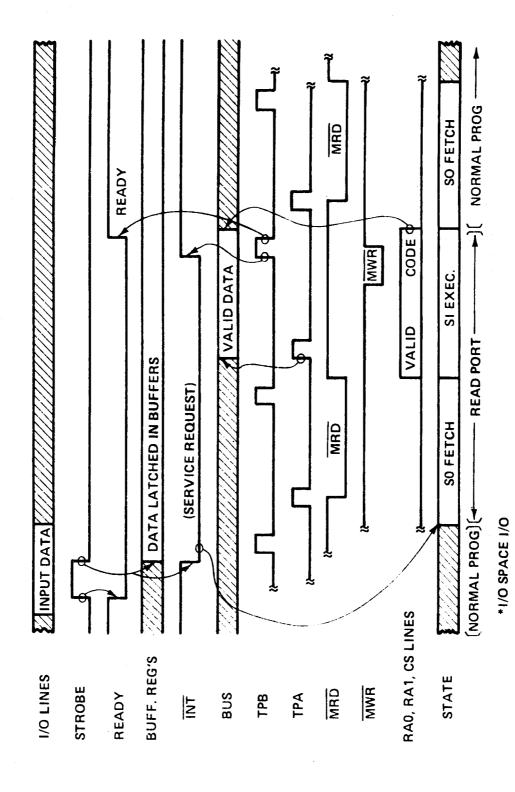

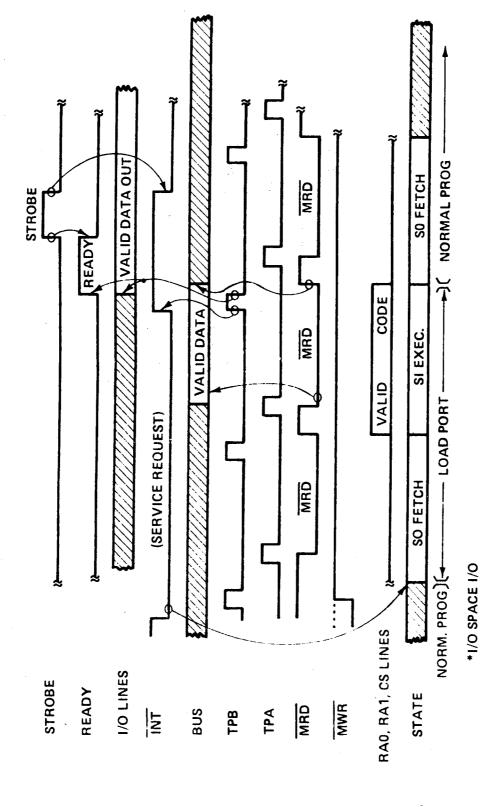

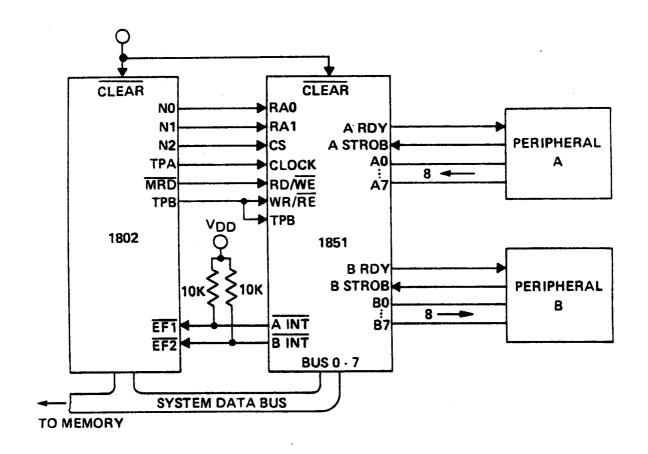

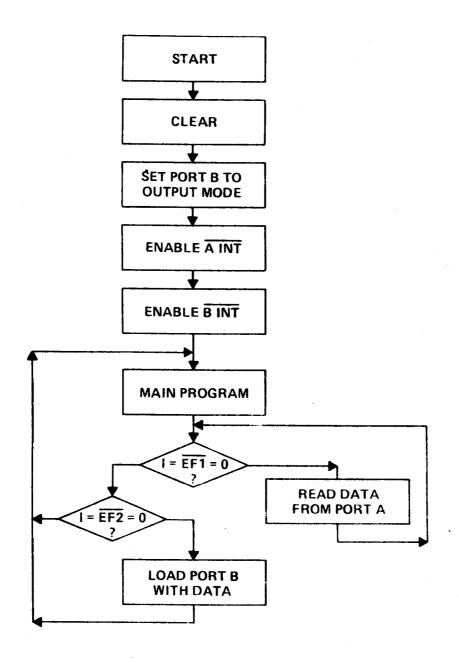

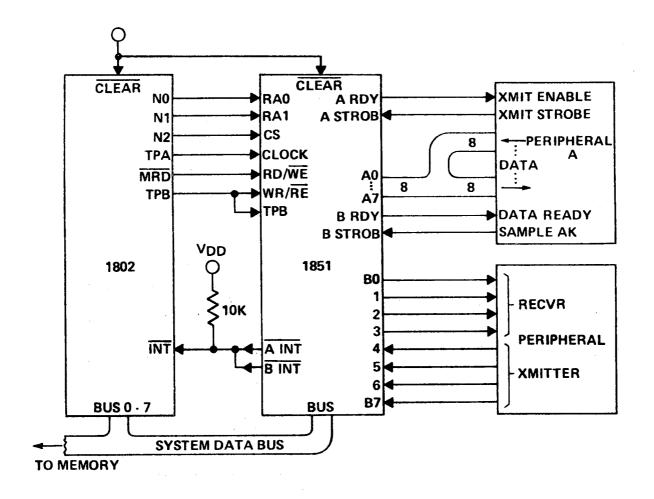

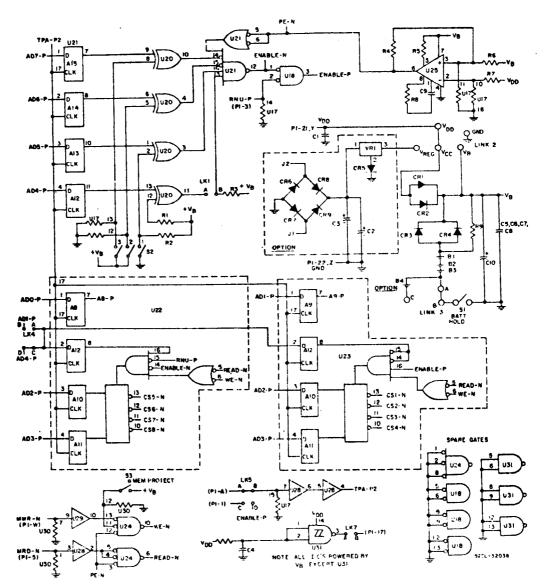

secutive memory locations since an input byte is automatically written into MR(X) as well as the D register. However, hardware can be devised that will automatically input both bytes when a single input instruction is executed. This circuitry, shown in Fig. 2, operates as follows: Execution of input instruction INP 1 will not directly read in a byte. However, it sets the Service Request (SR) of PORT 1, causing the next machine cycle to be given over to a DMA-IN operation which will read in PORT 1. The timing is such that two DMA cycles will actually occur, inputting PORT 1 and PORT 2 to sequential memory locations pointed to by R(0). The software for this sequence would consist only of:

SEX RO ..

Besides saving code, this approach is faster in the input operation (since DMA operations take only one machine cycle) than a sequence involving two inputs and a register increment.

A full 16-bit output can be obtained from the CDP1802 with one instruction, as shown in Fig. 3. Here, the contents of R(X) will be latched into PORTS 1 and 2 during the execute cycle of the output instruction. Since any one of the 16-bit registers can be output to the address lines, this technique is a very powerful one.

#### Reference

- "Optimizing Hardware/Software Trade-Offs in RCA CDP1802 Microprocessor Applications," L.A. Soloman, D. Block, RCA Solid State Application Note ICAN-6704.

- A more detailed discussion of this "register output" operation can be found in "Register Based Output Function for RCA COSMAC Microprocessors," N. Swales, RCA Solid State Application Note ICAN-6562.

Fig. 2—Circuit for automatic input of a 16-bit value to memory.

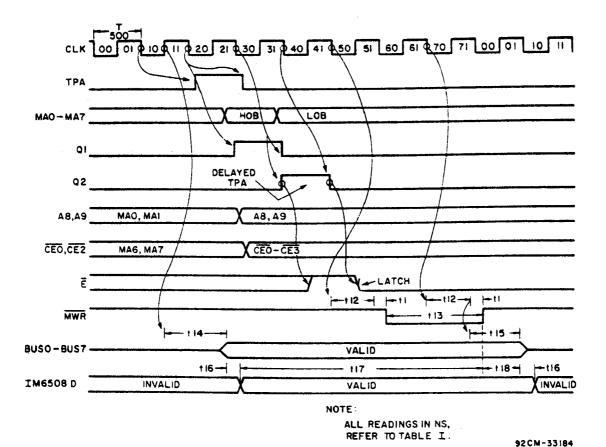

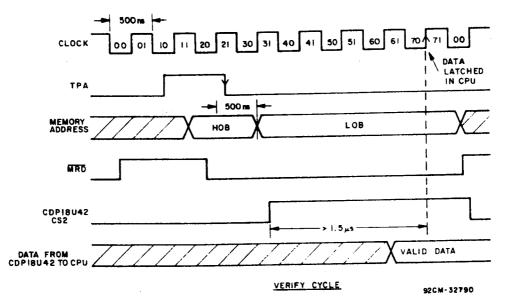

Fig. 3-Timing diagram for the circuit of Fig. 2.

When incorporating RCA Solid State Devices in equipment, it is recommended that the designer refer to "Operating Considerations for RCA Solid State Devices", Form No. 1CE-402, available on request from RCA Solid State Division, Box 3200, Somerville, N. J. 08876.

## CDP1804 and CDP1805 Processors Improve System Performance and Lower Chip Count

by J. Paradise

#### ST-6957

Prepared for and presented at Southcon/81

RCAISolid State Division Somerville, N.J. 08876 Printed in USA/11-80 Joseph Paradise RCA Solid State Division Somerville, N.J. 08876

The CDP1804 and CDP1805 processors are RCA's new introductions to the growing CDP1800 family of microprocessor and memory devices. These chips extend the capability of the CDP1802 microprocessor, both in higher performance and additional system functions, while maintaining upward software and hardware compatibility. To give the system designer a choice between flexibility and minimum chip count, two parts are offered: the CDP1805 for moderate cost and off-the-shelf availability, and the premium CDP1804 for custom VLSI system integration.

#### FUNCTIONAL DESCRIPTION

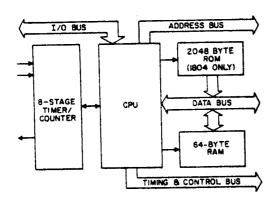

The CDP1804 is a CMOS, 8-bit, register-oriented microcomputer designed for use in a wide variety of general-purpose computing and control applications. It contains a 2048-byte mask-programmable ROM, 64 bytes of RAM, an 8-bit presettable down counter, and the same architecture as the CDP1802. The CDP1805 is identical to the CDP1804, with the exception that the ROM is left out for reasons of economy and flexibility. Both devices are capable of dc to 4-MHz operation at 5 volts over the commercial temperature range of -40°C to +85°C, and both have a voltage-range capability of from 4 to 10.5 volts. These added hardware and performance features, in addition to an enhanced instruction set, make the CDP1804 or CDP1805 a suitable choice for customers up-grading present CDP1802 systems for higher system performance or greater system integration or considering the CDP1800-series family for the first time. A block diagram of the CDP1804/CDP1805 processors is shown in Fig. 1.

1. CDP1804/CDP1805 block diagram.

92CS-33387

#### CDP1800 ARCHITECTURE IN SUMMARY

This section of the paper is designed for potential CDP1804/05 users unfamiliar with CDP1800-series architectural features, and explores the software and hardware aspects of data transfer and manipulation, and the control and timing interface to support devices. While established users of other 8-bit machines may find this architecture initially perplexing because of the extreme flexibility of assignments within register and memory space, familiarity with the device and its capabilities will pay off in compact code generation and efficient use of memory and I/O in most control-oriented applications.

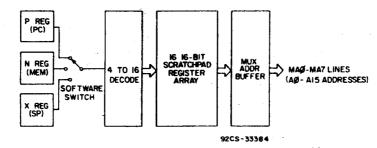

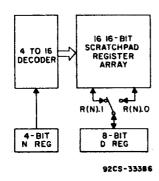

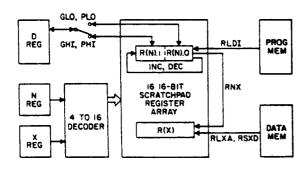

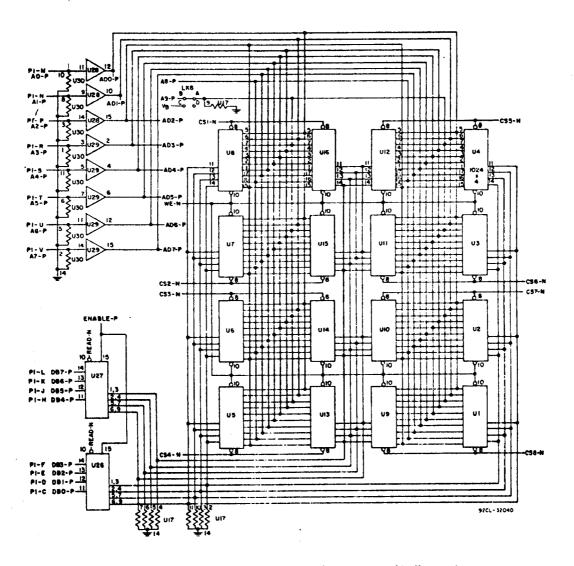

Scratchpad Register Array - The CDP1804/05 devices provide an indirect means of addressing memory through register assignment. Both devices contain sixteen 16-bit internal scratchpad registers (in addition to 64 bytes of RAM) that are user-programmable as program/subroutine counters, memory pointers, or stack pointers for memory addressing, Fig. 2. In addition, these same registers can hold data transferred to or from the accumulator (D register) by means of software instructions, Fig. 3. Finally, the register contents can be incremented or decremented for software loops or time delays.

Memory Addressing - When used to address memory, the registers are selected by software instructions that load 4-bit values into register selectors. The 4-bit P register selects a 16-bit scratchpad as the program counter, the 4-bit X register selects a scratchpad as the stack pointer, and the 4-bit Nregister selects a scratchpad as the memory pointer during an external data transfer, or as an operand during an internal data transfer (register-accumulator, register-register). Note that all 16 scratchpads are capable of addressing any of the 64K memory locations available to the CDP1804/05 processors; thus, stack space is unrestricted, scratchpads can point to subroutines located anywhere in memory space, and most registers can be dedicated for specific data storage or addressing tasks during subroutine or interrupt processing.

Addressing Modes - As a result of this register-oriented structure, addressing modes include direct, paged direct, immediate, indirect, and inherent. The direct mode applies to all branch instructions, which can

Common CDP1802/CDP1804/CDP1805 scratchpad register model, addresses.

Common CDP1802/CDP1804/CDP1805 scratchpad register model, data transfer.

cause conditional or unconditional jumps within the current page or anywhere in memory space. Indirect addressing allows transfer of data to or from either general memory or stack, depending on user allocation of memory space. The inherent mode allows for internal register modification with external memory inactive.

Instruction Set - In addition to memory reference instructions, the CDP1804/05 instruction set has a full complement of arithmetic and logic operations, conditional page and long branch instructions that test the contents of the accumulator and carry flag, register instructions that modify the contents of the internal scratchpads or register selectors, and I/O and interrupt handling instructions, Table I.

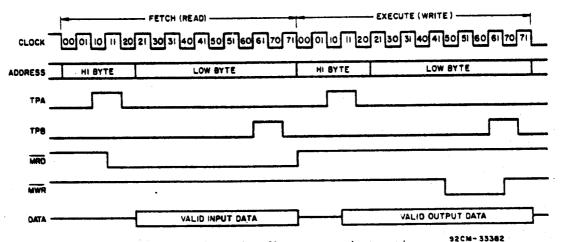

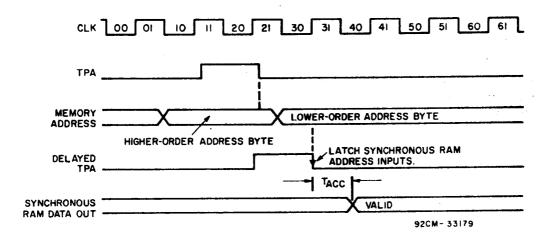

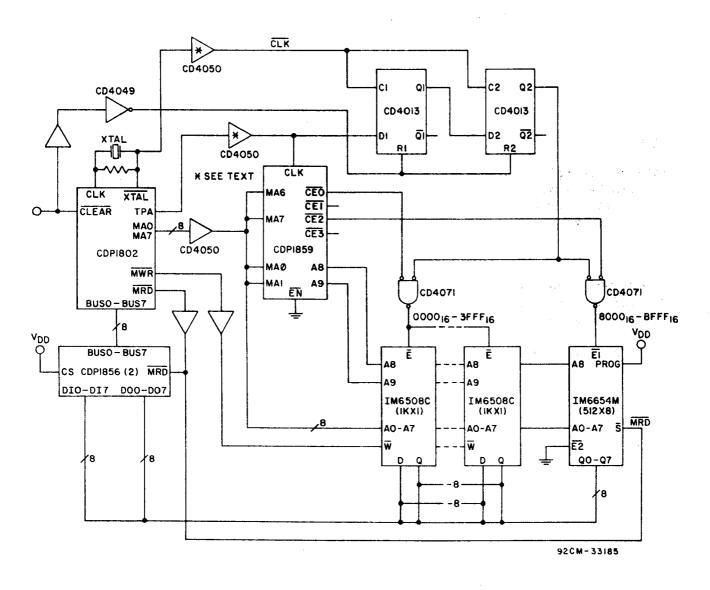

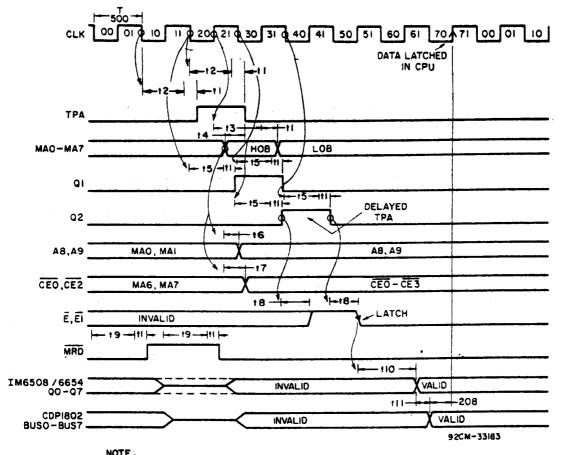

Bus Structure - The CDP1804/05 processors use a multiplexed address bus to address external memory. The high byte is generated first, with a TPA pulse provided to latch the byte into an external latch or a bus-compatible memory-support chip. The data bus is nonmultiplexed, with a TPB pulse provided to latch stable data into an I/O device. A separate, 3-bit, I/O address bus provides address selection for external peripheral chips.

Table I - Breakdown of 91 Instructions Common to CDP1802/04/05

| MEMORY TRANSFER     | 7  |

|---------------------|----|

| INTERNAL REGISTER   | 7  |

| LOGIC               | 10 |

| ARITHMETIC          | 12 |

| UNCONDITIONAL JUMPS | 4  |

| CONDITIONAL JUMPS   | 27 |

| CONTROL             | 7  |

| INTERRUPT CONTROL   | 3  |

| I/O TRANSFER        | 14 |

#### 9205-33392

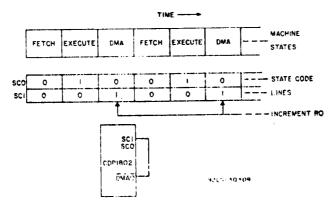

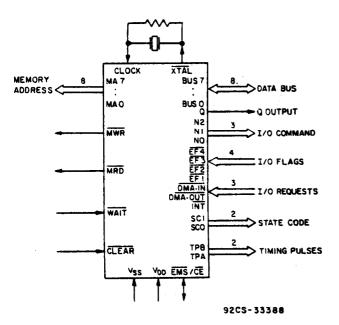

Control and Status Pins - Control pins are provided for DMA transfer (with register R(0) as the DMA counter), interrupt requests (with register R(1) storing the interrupt vector), four testable flags, and a single-bit software-controlled output port. Two state code lines provide machine status. Separate READ and URITE signals are provided for memory control, Fig. 4.

Execution Speed - System timing is derived from an external crystal. The crystal is divided so as to generate eight clock cycles per rachine cycle. A single FETCH and EXECUTE (16 clock cycles total) is all that is required for two-thirds of the instructions available with the CDP1804/05 devices. The result is a minimum instruction time of four microseconds at maximum frequency, Fig. 5.

#### CDP1800 ARCHITECTURE - USER ADVANTAGES -

The register-based orientation of the CDP1800-series architecture discussed in the previous section is its dominant feature, and

4. CDP1804/CDP1805 functional pinout.

CPU section to generate addresses and control signals for memory/I/O transfer in either a continuous or cycle-stealing mode. This DMA feature also allows the user to perform a real-time clock function without tying up significant software or execution time, Fig. 6. The I/O structure allows for stack transfer of data directly to and from memory, again bypassing the CPU in the process, and the special I/O lines, Flags and Q, allow for software polling of external events and single-bit output control, as well as the use of the lines in combination for bit-banging serial I/O.

## CDP1800 SERIES HARDWARE/SOFTWARE SUPPORT

An equally important advantage to potential CDP1804/05 users, besides architectural performance capabilities, is the availability of a complete line of compatible memory and I/O devices for efficient hardware designs, and easy-to-use tools to aid software development. The CDP1800-series is presently the

Basic dc timing diagram, one instruction cycle.

one not commonly found in the world of microprocessors. Once the user has mapped out a

plan to assign registers to perform specific

tasks, this flexibility provides him with a

rich variety of software techniques for

performing his required function. Flexible

register assignment results in such structures as multiple program counters for quick

subroutine calls, multiple stack pointers for

independent data and I/O stacks, and multiple

memory pointers that facilitate memory data

transfers and the adaptability of the

microprocessor to interpretive languages.

In addition, all CDP1800-series processors possess some unique hardware features that reduce system parts count and speed data transfer. The on-chip DMA counter allows the

broadest CMOS LSI line in the industry, and the software and debug support available allows users to reduce the significant soft ware burden required to program a micro processor family.

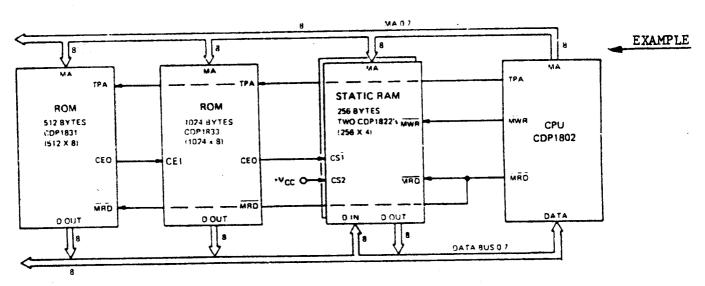

The list of support devices, Table II, for the CDP1800-series, which includes the CDP1802, CDP1804, and CDP1805 because of their compatibility, is highlighted by 12 RAM devices with capacities of from 32 to 4096 bits; ROM chips compatible with the CDP1800-series multiplexed bus structure, with user-programmed address decoders that uniquely define memory space without external decoding, and with identical pinout for system upgrade without board changes; EPROMs for system prototyping; and a wide variety of I/O devices

SCHEORCES DMA REQUEST EVERY THIRD MACHINE CYCLE. EACH DMA CYCLE MACHINE CTCLE EACH DMA CTCLE

INCREMENTS R(O). FOR FREQUENCY

SHOWN, R(O) OVERFLOWS ONCE PER

SECOND, WHICH CAN BE CHECKED

BY SOFTWARE.

#### 92CS - 33389

6. Application of DMA feature to generate real-time clock reference.

Table II - Major CDP1800-Series Support Components

|   | RAM                | <u>ıs</u> | SIMPL     | E 1/0                |

|---|--------------------|-----------|-----------|----------------------|

|   | CDPI82I            | IK X I    | CDP1852   | I/O PORT             |

|   | CDP1822            | 256 X 4   | CDP1853   | DECODER              |

|   | MWS5101            | 256 X 4   | CDP1856   | BUFFER               |

|   | CDPI823            | 128 X 8   | CDP1857   | BUFFER               |

|   | CDPI824            | 32 X 8    | CDP1858   | LATCH                |

|   | CDP1825            | IK X 4    | CDP1859   | LATCH                |

|   | MWS5II4            | IK X 4    | CDPI863   | COUNTER              |

| × | CDPI826            | 64 X 8    | CDP1866   | LATCH                |

|   |                    |           | CDP1867   | LATCH                |

|   |                    | _         | CDP1872   | I/O PORT             |

|   | ROM                | <u>s</u>  | CDPI873   | DECODER              |

|   | CDPI83I            | 512 X 8   | CDP1874   | I/O PORT             |

|   | CDPIB32            | 512 X 8   | CDP1875   | I/O PORT             |

|   | CDP1833            | IK X 8    |           |                      |

|   | CDPI834            | IK X 8    |           |                      |

|   | CDP1835<br>MWS5316 | 2K X 8    | COMP      | LEX I/O              |

| * | M M 30310          | ENAG      | CDPI85I   | PROG I /O            |

|   |                    |           | CDPI854A  | UART                 |

|   | EPR                | OMS       | CDP1855   | MDU                  |

|   | CDPI8U42           | 256 X 8   | CDP1869   | CRT CONTROLLER       |

| × | MWS57U58           | IKX8      | CDP1870   | CRT CONTROLLER       |

|   |                    |           | CDPI871   | KEYBOARD ENCODER     |

|   |                    |           | CDPI876   | CRT CONTROLLER       |

|   |                    |           | * CDPI877 | INTERRUPT CONTROLLER |

|   |                    |           | * COLIGII | MIERROFI CONTROLLER  |

\* RESERVED NUMBER FOR 1981 PRODUCTION DEVICES

92CS-33383

ranging from simple buffers and latches to complex peripherals such as multiport programmable I/O, UART's, math chips, and CRT controllers.

Software support is available from products that range from simple prototyping kits to complete development systems. High-level languages, including micro FORTH, PL/M, and BASIC, are available to reduce software development time. In-circuit emulation, through the use of the "Micromonitor," provides comprehensive debug and evaluation capability, either in conjunction with a development system or for standard-alone use in the field. Finally, a complete line of CMOS single-board computers and peripheral subsystems, designed around products in the CDP1800-series family, are available to further ease the cost and the turn-around time of hardware implementation, Table III.

Table III - Major CDP1800-Series System Support

#### **DEVELOPMENT SYSTEM**

- COSMAC SYSTEM IV (CDP185008)

- CRT-BASED SYSTEM CONTAINING: 64K MEMORY

- - . DUAL FLOPPY-DISK DRIVES

- IN-CIRCUIT EMULATION (MICROMONITOR)

BUILT-IN PROM PROGRAMMER

COMPLETE DISK OPERATING SYSTEM

- - . LEVEL I, LEVEL II ASSEMBLER

- · MACROASSEMBLER

- . FULL-SCREEN EDITOR AND TEXT EDITOR

- · MICROMONITOR OPERATING SYSTEM (MOPS) · PROM-PROGRAMMER OPERATING SOFTWARE

#### SOFTWARE (OPTIONAL)

- . BASIC 1 (FIXED POINT) INTERPRETER/COMPILER

- BASIC 2 (FLOATING POINT) INTERPRETER

- PLM-1800 COMPUER

- . FIXED AND FLOATING POINT MATH SUBROUTINES

#### MICROBOARDS -- SINGLE BOARD MICROCOMPLITERS

- . COORDINATED SET OF COMPUTER, MEMORY AND I/O BOARDS

- CDP18S606 1804/1805 EVALUATION BOARD CONTAINS:

1804 CPU W/2.47 MHZ CLOCK

- 2K BYTES RAM (FOR 1804 ROM SIMULATION)

- 2 EACH ROM/EPROM SOCKETS

- . 2 EACH PARALLEL I/O PORTS

- . RS232C SERIAL PORT (UART)

#### CDP1804/05 ENHANCEMENTS

The preceding discussion has dealt with features and advantages that are common to the CDP1802, CDP1804, and CDP1805, The following sections describe specific enhancements to the CDP1802: increased memory, timer-counter implementation, standard call and return instructions, and enhanced 16-bit data manipulation, all of which should be of particular usefulness to those who are already familiar with CDP1802 capabilities and the advantages of hardware and software enhancements in their system designs.

#### Memory

A significant feature of the upgraded CDP1804 is its memory expandability, which is not compromised as in some other single-chip microprocessors. The same 64K memory address space is available, with 2K of ROM and 64 bytes of RAM on-board. The large on-board ROM size is sufficient for many application programs, and it can hold special firmware such as the CDP18S827 floating-point binary arithmetic subroutine, or a budget interpreter such as TINY BASIC. The internal RAM provides enough locations for stack and auxiliary scratchpad usage; data-acquisition applications can take advantage of the larger memory address space for outboard RAM. Note that both internal ROM and RAM have maskprogrammable address spaces, with an EMS signal provided to indicate when external memory is being addressed.

The CDP1805 has the same RAM complement and expandability features as the CDP1804. Since the device is an off-the-shelf part, its RAM is accessed through a  $\overline{\text{CE}}$  input that replaces the CDP1804 EMS output. In general, the user will find the absence of ROM on the CDP1805 an advantage in many system applications because of the trend to larger and larger ROM programs in increasingly sophisticated systems. The absence of the ROM allows the user great flexibility in designing his system, and may well provide the most cost-effective approach for the majority of applications. Thus, the CDP1805 should be chosen when anticipated ROM program space exceeds that of the capacity of the CDP1804, when prototyping an experimental application with EPROM, when the application software can change, or when the user is willing to trade off cost for increased chip count.

#### Timer/Counter

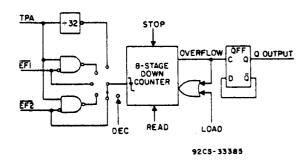

An additional hardware feature of the CDP1804/05 devices, besides on-board memory, is an 8-stage presettable down counter, Fig. 7. This is a full-function timer/counter,

7. CDP1804/CDP1805 timer/counter\_model.

with inputs available from an external source or a scaled internal clock, and output overflow indication through the external Q line or an internal counter interrupt request. The counter makes use of ten linked opcode instructions to perform its control functions and to program the counter for its operational modes. LOAD, READ, STOP, and DECREMENT control instructions provide manual control and allow the counter to be used to generate a programmable time delay. Three running modes can be programmed with five additional instructions; the modes are:

- TIMER with the input derived from the CDP1804/05 TPA pulse divided by 32, which allows its use as a time base for real-time applications.

- EVENT COUNTER with the input from l of 2 flag lines (software selectable), for single or dual-channel event counting.

- 3. PULSE DURATION MEASUREMENT with the input again from a flag line, with the counter value representing the pulse width at the input. Because two inputs can be sequentially applied, comparison measurements can be made.

In conjunction with each of these modes, a tenth instruction, ETQ, can generate a programmable square wave or provide control to external peripherals by toggling the Q output on every counter overflow.

In addition to the ten timer/counter functions, six additional instructions allow arbitration between external and counter interrupts. Two instructions each are provided for interrupt masking and unmasking, while two others allow for software polling to determine the interrupt source.

#### Standard Call and Return

The most significant software enhancement of the CDP1804/05 devices over the CDP1802 is the addition of single CALL and RETURN instructions, which save both software and time, and free-up internal scratchpad registers for other uses, Table IV. These instructions, SCAL and SRET, are slightly different than those of other microprocessor families, primarily to allow the user to pass in-line data from the main program or calling routine to the target subroutine. Direct addressing is incorporated as with other families: however, the main program counter is exchanged with a designated scratchpad, and it is the scratchpad contents that are saved on the stack. This technique allows the original PC to point to data following the call

Table IV - Performance Comparisons-Subroutine

Call and Return for CDP1802/04/05

Implemented with Various Techniques

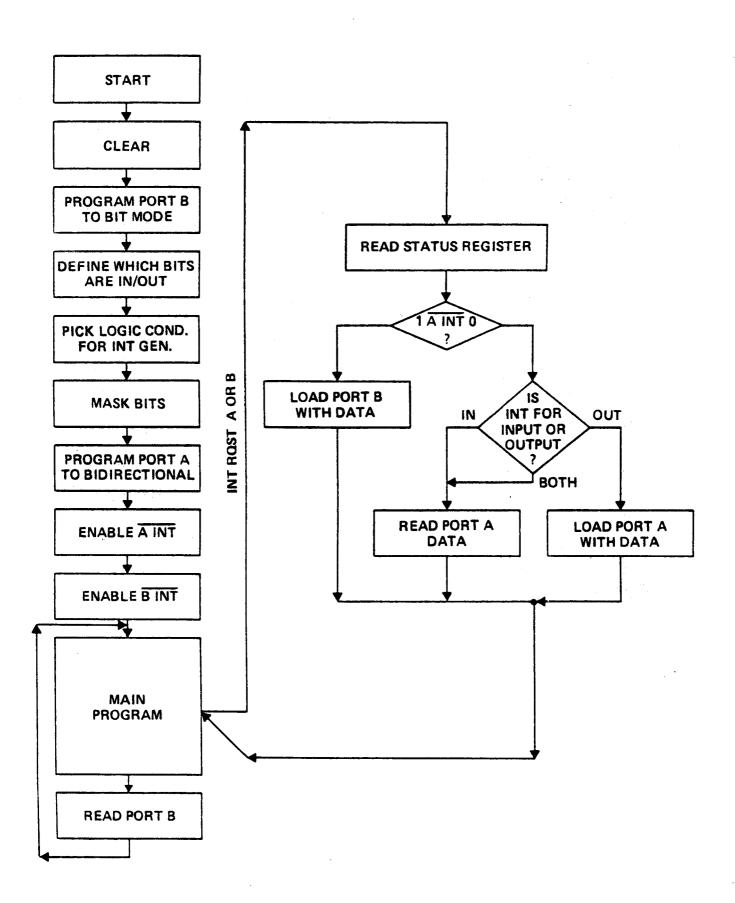

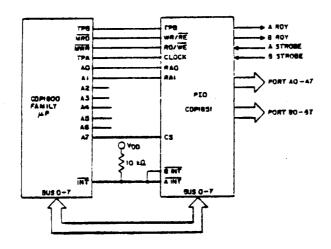

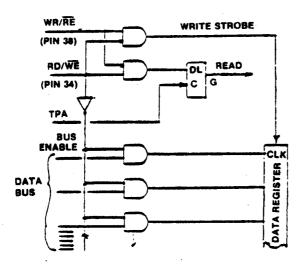

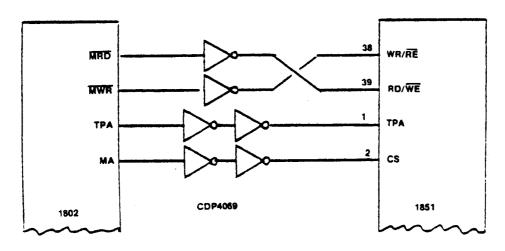

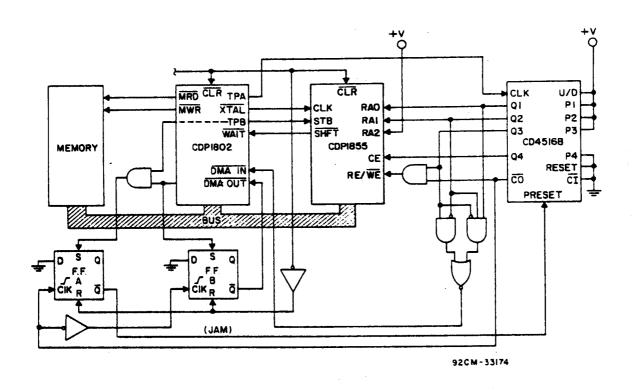

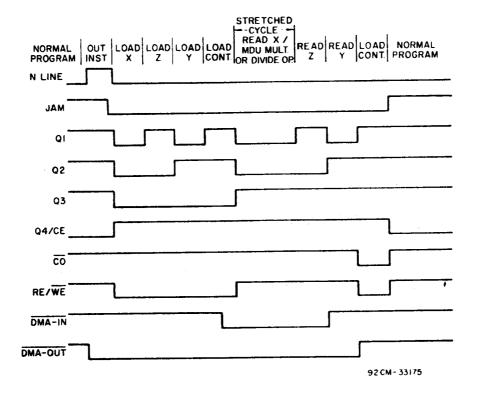

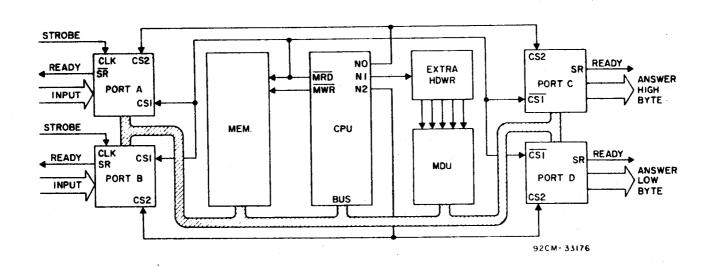

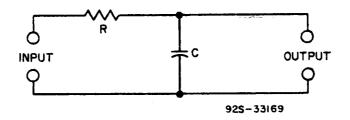

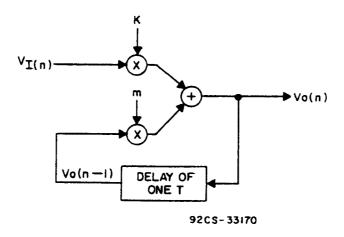

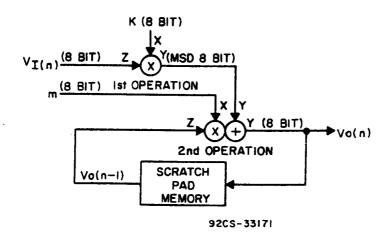

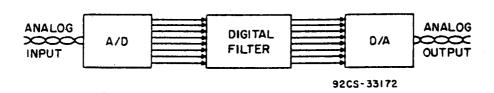

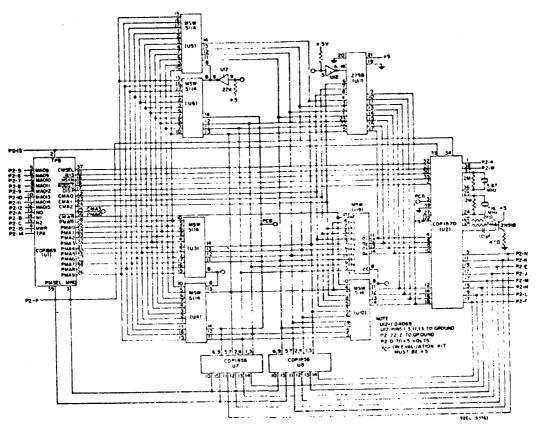

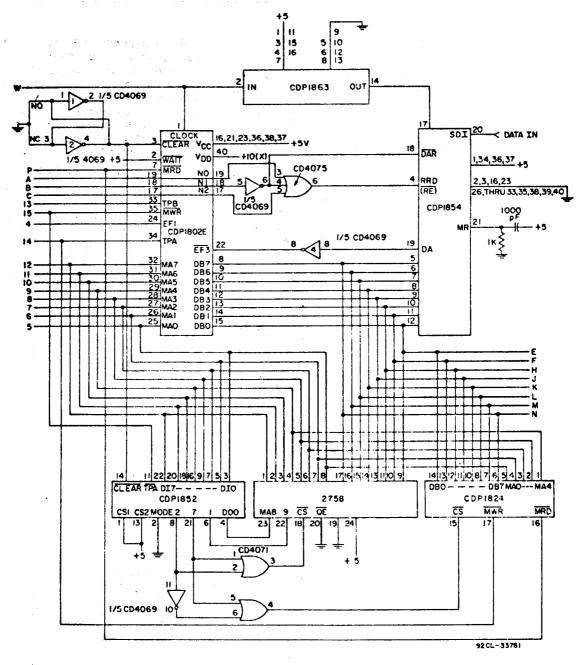

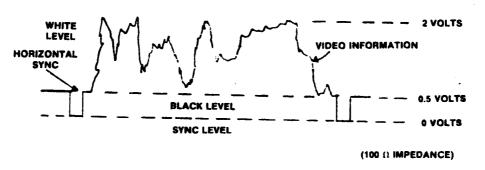

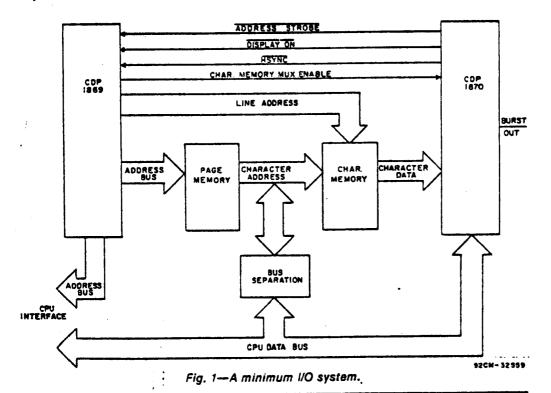

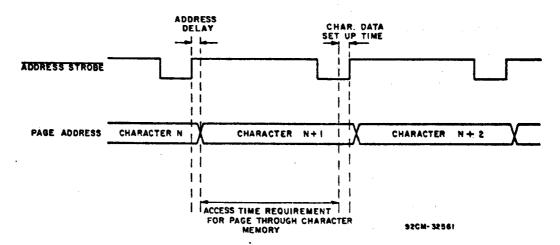

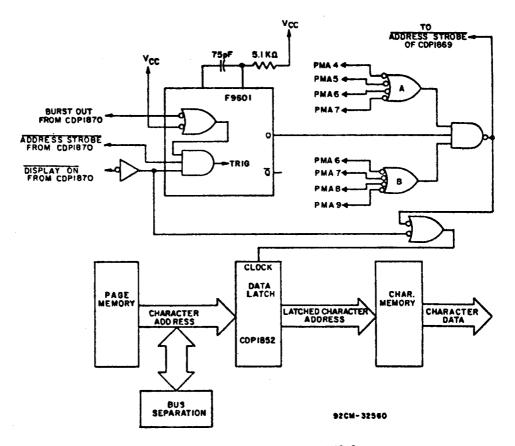

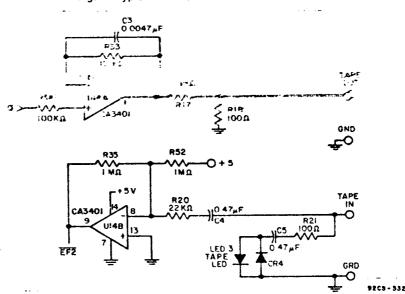

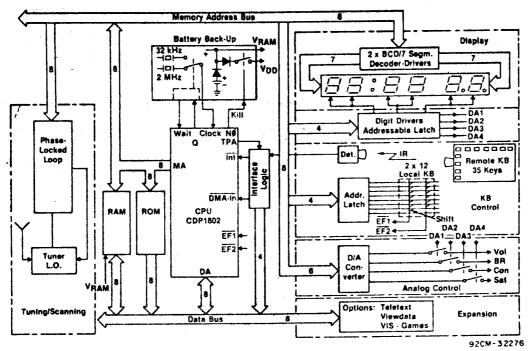

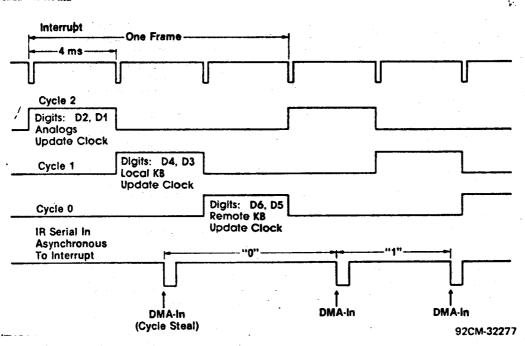

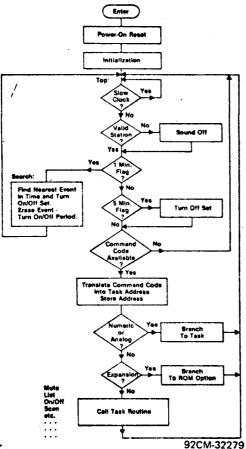

|                                                      | 1802 SOFTWARE<br>"SCRT"<br>TECHNIQUE | 1802 SOFTWARE<br>"SEP"<br>TECHNIQUE | 1804/05 SOFTWARE<br>SCAL / SRET<br>INSTRUCTIONS | 1804/05 SOFTWARE<br>"SEP"<br>TECHNIQUE |